جدول المحتويات:

- الخطوة 1: مخطط الكتلة

- الخطوة 2: مبدأ العملية

- الخطوة 3: تطبيق المنطق

- الخطوة 4: حل الجمود

- الخطوة 5: تكوين الجهاز - دائرة Matrix0

- الخطوة 6: تكوين الجهاز - منطق توقيت SPI

- الخطوة 7: تكوين الجهاز - خصائص مكونات Matrix0

- الخطوة 8: تكوين الجهاز - دائرة Matrix1

- الخطوة 9: تكوين الجهاز - عداد ثنائي 3 بت

- الخطوة 10: تكوين الجهاز - مقارنة منطق 3 بت

- الخطوة 11: تكوين الجهاز - منطق المقارنة الرقمية والتسجيل المؤقت

- الخطوة 12: تكوين الجهاز - خصائص مكونات Matrix1

- الخطوة 13: النتائج

- مؤلف John Day day@howwhatproduce.com.

- Public 2024-01-30 07:37.

- آخر تعديل 2025-01-23 12:53.

تتعامل أنظمة التحكم والأجهزة ذات الصلة مع مصادر طاقة متعددة ، مثل خطوط التحيز أو البطاريات ، ويجب أن تتبع أعلى خط (أو أدنى) بين مجموعة معينة.

على سبيل المثال ، يتطلب تبديل الحمل في نظام يعمل بالطاقة "بطاريات متعددة" أن يراقب النظام إما الحد الأدنى أو الحد الأقصى للجهد بين مجموعة البطاريات (الحد الأقصى أو الحد الأدنى كدالة لخوارزمية التحويل المعينة) وتوجيه الحمل ديناميكيًا إلى أنسب مصدر في الوقت الحقيقي. بدلاً من ذلك ، قد يحتاج النظام إلى فصل البطارية ذات الجهد المنخفض بشكل مؤقت من أجل الشحن المناسب.

مثال آخر هو نظام الطاقة الشمسية الحديث ، حيث تم تجهيز كل لوحة شمسية بآلية إمالة ودائرة تتبع شمسية (توفر الأخيرة معلومات موقع الشمس لتوجيه اللوحة). باستخدام معلومات الجهد الأقصى ، يمكن ضبط كل موضع لوحة شمسية بدقة على أساس لوحة السلسلة التي تقدم فعليًا أعلى جهد ناتج ، وبالتالي تحقيق مستوى أعلى من تحسين الطاقة.

هناك العديد من العلامات التجارية المختلفة للدوائر المتكاملة التجارية (بشكل أساسي المتحكمات الدقيقة) التي يمكنها من حيث المبدأ تنفيذ متابع أقصى جهد. ومع ذلك ، فهي تتطلب برمجة وتكون أقل فعالية من حيث التكلفة من حل الإشارات المختلطة. يمكن أن يؤثر استكمال تصميم Dialog GreenPAKTM بشكل إيجابي على القدرة على تحمل التكاليف وحجم ونمطية التصميم. يستغل هذا التصميم ميزة دمج الدوائر التناظرية والرقمية في شريحة واحدة.

في هذا Instructable ، يتم تنفيذ الواجهة الأمامية التناظرية والمنطق الرقمي المطلوبين لتنفيذ جهاز تحديد الجهد الأقصى (أو في النهاية) بين ثمانية مصادر متميزة.

لتنفيذ جهاز مراقبة الجهد الأقصى / الدقيقة التناظري ذي 8 قنوات ، يتم استخدام SLG46620G.

فيما يلي وصفنا الخطوات اللازمة لفهم كيفية برمجة الحل لإنشاء جهاز مراقبة الجهد الأقصى / الدقيقة التناظري المكون من 8 قنوات. ومع ذلك ، إذا كنت ترغب فقط في الحصول على نتيجة البرمجة ، فقم بتنزيل برنامج GreenPAK لعرض ملف تصميم GreenPAK المكتمل بالفعل. قم بتوصيل GreenPAK Development Kit بجهاز الكمبيوتر الخاص بك واضغط على البرنامج لإنشاء 8 قنوات مراقبة أقصى / دقيقة للجهد التناظري.

الخطوة 1: مخطط الكتلة

يوضح الشكل 1 الرسم البياني العالمي للنظام المنفذ.

يتم مضاعفة سلسلة تصل إلى 8 مصادر جهد متغير وربطها بوحدة ADC من GreenPAK متصلة بتصميم داخلي مخصص قادر على اختيار المصدر ذي الجهد العالي فيما يتعلق بالآخرين. يقوم المنطق الداخلي بإخراج هذه المعلومات للعرض أو لمزيد من المعالجة.

يعتمد التصميم على منتج GreenPAK SLG46620G ، لأنه يتضمن جميع وحدات البناء التناظرية والرقمية اللازمة للتطبيق. في هذا التنفيذ ، يتم فحص الصفيف عن طريق معدد إرسال تناظري ADG508 مدفوعًا مباشرة بواسطة GreenPAK IC.

معلومات الخرج هي رقم رقمي 3 بت يتوافق مع رقم مصدر الجهد عند الحد الأقصى للجهد. تتمثل الطريقة المباشرة للحصول على هذه المعلومات في إظهار الرقم عن طريق عرض من 7 أجزاء. يمكن تحقيقه بسهولة عن طريق توصيل الإخراج الرقمي لـ SLG46620G ببرنامج تشغيل عرض من 7 أجزاء ، مثل حل GreenPAK الموضح في المرجع أو بـ 74LS47 IC المشترك.

الدائرة المعروضة تبحث عن أقصى جهد. لتحويل التصميم إلى مكتشف جهد أدنى ، يجب إضافة دائرة تكييف مسبق بسيطة بين مُضاعِف الإرسال التناظري ومدخل GreenPAK التناظري ، مع طرح خرج مُضاعِف الإرسال من جهد مرجعي 1 فولت.

الخطوة 2: مبدأ العملية

يهدف التصميم إلى تحديد المصدر ذي الجهد الأقصى ، وبالتالي يتم إجراء مسح على المصفوفة بأكملها أثناء تخزين آخر قيمة قصوى ومقارنتها بالقيمة التالية في الإدخال (والتي تنتمي إلى مصدر الجهد التالي في الفحص).

في ما يلي سوف نشير إلى تسلسل تعدد إرسال كامل على طول جميع المدخلات كـ "مسح" أو "حلقة".

لا يتم إجراء المقارنة بين قيمتين عن طريق مكونات ACMP (مع ذلك ، متوفرة في SLG46620G) ، ولكن بواسطة وحدة DCMP ، بمجرد أن يتم ترقيم القيم على التوالي. هذا أسلوب متقدم ومكرر تم تناوله أولاً في المرجع.

يوضح الشكل 2 كيفية تنظيم SLG46620G لهذا التصميم.

تنتقل إشارة الإدخال التناظرية إلى إدخال ADC من خلال مكون PGA بمجموعة مكاسب قدرها 1. يمكن أيضًا العثور على إعدادات كسب مختلفة للعثور على أفضل تطابق مع إلكترونيات التكييف الأمامية المخصصة لتعيين الفولتية المدخلة إلى 0-1 فولت نطاق وحدة GreenPAK ADC.

تعمل ADC في الوضع أحادي النهاية وتحول الإشارة التناظرية إلى رمز رقمي 8 بت ، والذي يتم نقله بعد ذلك إلى وحدة DCMP. يتم إدخال الكود الرقمي أيضًا في كتلة SPI ، التي تم تكوينها كمخزن ADC / FSM مؤقت ، حيث يمكن تخزين رمز رقمي ولن يتغير حتى تأتي النبضات التالية إلى إدخال SPI CLK. لاحظ أن كتلة منطق مخصصة تقوم بتشغيل إدخال SPI CLK. سنحقق في هذا الجزء لاحقًا ، لأن هذا هو المنطق "الأساسي" المسؤول عن التشغيل السليم. يتم تخزين رمز رقمي جديد في وحدة SPI فقط إذا كان ينتمي إلى جهد الدخل الأقصى الفعلي.

يتم استخدام مكون DCMP لمقارنة بيانات ADC الحالية مع الفائز الأخير (وهذا هو آخر حد أقصى تم العثور عليه) المخزنة في كتلة SPI. سيولد نبضًا عند خرج OUT + عندما تكون بيانات ADC الجديدة أكبر من البيانات السابقة. نستخدم إشارة OUT + لتحديث كتلة SPI بالفائز الجديد.

تقود إشارة الساعة العالمية تحويلات ADC والتوقيتات العامة. بمجرد إجراء التحويل ، تنبض إشارة خرج INT الخاصة بـ ADC ، بالتنسيق مع إخراج البيانات المتوازية ADC. نستخدم ناتج INT أيضًا لزيادة عداد ثنائي مكون من 3 بتات ، يتم تنفيذه بواسطة DFFs في Matrix1 ، وهو أمر مفيد لثلاثة أسباب:

1. تعالج خطوط إخراج العداد المضاعف التناظري الخارجي ، وبالتالي تخدم جهد الدخل التالي إلى ADC ؛

2. يتم تجميد العدد في سجل 3 بت (تم تنفيذه في Matrix1) لتخزين الفائز المؤقت أثناء المسح ؛

3. يتم فك تشفير العد لتحديث سجل 3 بتات ثاني (تم تنفيذه في Matrix0) بمجرد اكتمال المسح.

الخطوة 3: تطبيق المنطق

توفر وحدة ADC بشكل تسلسلي بيانات محولة لجميع الفولتية المدخلة ، واحدة تلو الأخرى ، إلى أجل غير مسمى. بمجرد معالجة المضاعف 0b111 (الرقم العشري 7) ، ينتقل العداد إلى 0b000 (الرقم العشري 0) وبالتالي يبدأ مسحًا جديدًا لجهود الإدخال.

أثناء الفحص ، يتم إنشاء إشارة خرج ADC INT عندما يكون إخراج البيانات المتوازي صالحًا. عندما تنبض هذه الإشارة ، يجب أن يتحول مُضاعِف الإرسال التناظري إلى الإدخال التالي ، مع تزويد PGA بالجهد المقابل. لذلك ، فإن خرج ADC INT هو إشارة تسجيل الوقت المباشر للعداد الثنائي المكون من 3 بتات في الشكل 2 ، والذي تتناول كلمته الخرجية المتوازية المكونة من 3 بتات مُضاعِف الإرسال التناظري الخارجي ("V select" في الشكل 1).

دعنا الآن نشير إلى مثال حيث من المفترض أن يكون لجهود المدخلات العلاقات التالية:

أ) V0 <V1 <V2

ب) V2> V3، V4

ج) V5> V2

يمثل الشكل 3 الإشارات الرئيسية المشاركة في آلية القرار الأقصى.

نظرًا لأنه يتم تسجيل البيانات في النهاية في سجل المخزن المؤقت SPI بشكل متزامن مع نبضات INT ، توجد نافذة مقارنة حيث تتم مقارنة محتوى المخزن المؤقت SPI بنتيجة تحويل ADC التالية. ينتج عن هذا التوقيت المعين توليد نبضات OUT + في خرج DCMP. يمكننا الاستفادة من هذه النبضات لتحميل قيم جديدة في سجل المخزن المؤقت SPI.

كما يتضح من خط بيانات المخزن المؤقت SPI في الشكل السابق ، يحتوي سجل SPI دائمًا ، مرة تلو الأخرى ، على أكبر قيمة بين المدخلات الثمانية ويتم تحديثه فقط عند اكتشاف قيمة أكبر بواسطة وحدة DCMP (بالإشارة إلى DCMP OUT + خط الإخراج للمخطط ، تتسبب النبضات المفقودة في بقاء V2 مغلقًا في السجل حتى مقارنته بـ V5).

الخطوة 4: حل الجمود

إذا كان المنطق الذي تم تنفيذه كما هو موضح أعلاه ، فمن الواضح أننا سنصطدم بحالة توقف تام: النظام قادر فقط على اكتشاف الفولتية الأعلى من ذلك المقابل لما يتم تخزينه في سجل المخزن المؤقت SPI.

هذا صحيح أيضًا في حالة انخفاض هذا الجهد ، ثم يصبح دخل آخر أقل من ذلك حتى الآن هو الأعلى: لن يتم اكتشافه أبدًا ، وقد تم شرح هذا الموقف بشكل أفضل في الشكل 4 حيث يوجد 3 جهد دخل فقط من أجل وضوح.

في وقت التكرار 2 ، يسقط V3 و V1 هو الجهد الأقصى الفعلي. لكن وحدة DCMP لا توفر نبضًا لأن البيانات المخزنة في سجل المخزن المؤقت SPI (المقابل لـ 0.6 فولت) أكبر من تلك المقابلة لـ V1 (0.4 فولت).

بعد ذلك ، يتصرف النظام كمكتشف أقصى "مطلق" ولا يقوم بتحديث الإخراج بشكل صحيح.

هناك طريقة جيدة للتغلب على هذه المشكلة وهي فرض إعادة تحميل البيانات في SPI Buffer Register عندما يكمل النظام دورة استقصاء كاملة لجميع القنوات.

في الواقع ، إذا كان الجهد عند هذا الإدخال لا يزال أعلى ، فلن يتغير شيء وسيستمر التحكم بأمان (بالإشارة إلى الشكل 4 أعلاه ، هذه هي حالة تكرار الحلقة 0 و 1). من ناحية أخرى ، إذا انخفض الجهد عند هذا الإدخال عن طريق الصدفة إلى قيمة أقل من إدخال آخر ، فإن إعادة تحميل القيمة تعطي إمكانية لوحدة DCMP لإنتاج نبضة خارج + عند مقارنتها بالقيمة القصوى الجديدة (هذا هو حالة تكرار الحلقة 2 و 3).

قطعة من الدائرة المنطقية ضرورية للتغلب على المشكلة. يجب أن تولد إشارة ساعة إلى مكون SPI عندما تصل الحلقة إلى الحد الأقصى الفعلي للإدخال ، وبالتالي إجبارها على إعادة تحميل كلمة البيانات المحدثة في SPI Buffer Register. سيتم مناقشة ذلك في القسمين 7.2 و 7.6 أدناه.

الخطوة 5: تكوين الجهاز - دائرة Matrix0

يحتوي SLG46620G على كتلتين من المصفوفات ، كما هو موضح في الشكل 2. توضح الأشكال التالية تكوينات الجهاز المعنية.

الجزء العلوي من الدائرة هو "Loop Register" المحقق بـ 3 DFFs (DFF0 و DFF1 و DFF2). يتم تحديثه بعد كل حلقة من مُضاعِف الإدخال لإرسال الرقم الثنائي "للفائز" إلى برنامج تشغيل العرض ذي الأجزاء السبعة ، وهو المدخل ذو الجهد الأعلى في المسح الأخير. تأتي كل من الساعة إلى DFFs والبيانات من المنطق المطبق في Matrix1 من خلال المنفذ P12 و P13 و P14 و P15 على التوالي.

الجزء السفلي هو الواجهة الأمامية التناظرية مع إدخال عند Pin 8 و PGA مع كسب x1. ينتقل خرج ADC INT إلى منطق تسجيل الوقت SPI وإلى Matrix1 عبر المنفذ P0 ، حيث سيكون بمثابة إشارة ساعة للعداد المطبق.

يتم تسمية مخرجات البيانات المتوازية ADC و SPI على التوالي NET11 و NET15 ليتم توصيلها بمكون DCMP في Matrix1.

الخطوة 6: تكوين الجهاز - منطق توقيت SPI

كما أشرنا سابقًا في قسم "تنفيذ المنطق" ، يتم تحديث سجل المخزن المؤقت SPI في كل مرة تولد فيها مقارنة بين القيمة المخزنة الفعلية وبيانات تحويل ADC الجديدة نبضًا عند إخراج DCMP OUT +.

يتم ضمان سلامة الإشارة إذا تم تحرير هذه الإشارة بإخراج ADC INT. هذا يتجنب أي ارتفاع أو إثارة زائفة.

لقد أكدنا أيضًا أنه لتخطي حالات الجمود ، يجب تحديث SPI Buffer عندما تصل الحلقة إلى بيانات الفائز الفعلية.

ثم توجد ثلاث إشارات في اللعبة لتسجيل التوقيت المناسب لمؤشر SPI:

1. إخراج ADC INT (LUT0-IN1)

2. DCMP OUT + output (LUT0-IN0 عبر المنفذ P10)

3. العد يساوي إشارة المزلاج (LUT0-IN2 عبر المنفذ P11)

الأولان هما AND-ed وكلاهما OR-ed مع الأخير في LUT0 ، والذي تم تكوين تنفيذه كما في الشكل 6.

الخطوة 7: تكوين الجهاز - خصائص مكونات Matrix0

توضح الأشكال 7-10 نوافذ خصائص المكونات المتبقية التي تنتمي إلى Matrix0.

الخطوة 8: تكوين الجهاز - دائرة Matrix1

الخطوة 9: تكوين الجهاز - عداد ثنائي 3 بت

يحتوي الجزء العلوي من الدائرة على عناصر منطقية ، بشكل أساسي عداد ثنائي مكون من 3 بتات تم تسجيله بواسطة خرج ADC INT ، كما تمت مناقشته بالفعل. يتم تنفيذ هذا العداد باستخدام تخطيطي "قياسي" تمامًا كما هو موضح في الشكل 12.

يتم تحقيق هذا العداد في تصميمنا عن طريق Flip-Flops DFF9 و DFF10 و DFF11 و INV1 و LUT4 و LUT8. ناتج DFF9 هو LSB بينما DFF11 هو MSB كما هو موضح في الشكل 13.

تم تكوين LUT4 على أنه XOR بينما ينفذ LUT8 منطق AND-XOR في الشكل 12.

تذهب مخرجات العداد إلى ثلاثة دبابيس إخراج رقمية لمعالجة المضاعف التناظري الخارجي.

يفك LUT10 رمز العداد عند اكتمال المسح ويغذي نبضة إلى Matrix0 عبر DLY8 والمنفذ P12. يتم تحقيق ذلك ببساطة عن طريق AND-ing مخرجات العداد ، وبالتالي فك تشفير الرقم 7 dec (0b111 ثنائي ، نهاية الحلقة).

الخطوة 10: تكوين الجهاز - مقارنة منطق 3 بت

يوضح الشكل 15 الدائرة المستخدمة لاكتشاف متى تتكرر الحلقة في العنوان "الفائز" الحالي. في هذه الحالة ، كما تمت مناقشته بالفعل ، يجب أن تفرض النبضة الرقمية إعادة تحميل نتيجة ADC الحالية لحل حالة الجمود المحتملة.

يتم تخزين العنوان "الفائز" في السجل المؤقت لـ Matrix1 (انظر أدناه) ، بينما يتم إخراج العنوان الحالي بواسطة العداد الثنائي.

توفر بوابات XNOR ناتجًا حقيقيًا (منطق 1 أو "مرتفع") عندما يكون كلا المدخلين متساويين. وتعطينا هذه الإشارة لجميع البتات (LUT9) نبضًا عندما يكون كل من الرموز الثنائية متماثلًا. يمكن العثور على تفاصيل حول بوابات XOR كمدقق تكافؤ في المرجع.

يتم تمرير إشارة "Counter-equals-Latch" إلى Matrix0 عبر المنفذ P11.

الخطوة 11: تكوين الجهاز - منطق المقارنة الرقمية والتسجيل المؤقت

يوضح الجزء السفلي من الشكل 11 (الموضح في الشكل 16) كتلة DCMP ، وهي جزء صنع القرار من هذا التصميم.

DFF6 و 7 و 8 تشكل سجل 3 بت لتخزين رقم الإدخال المؤقت "الفائز" أثناء تشغيل الحلقة. المدخلات إلى Flip-Flops هي مخرجات العداد الثنائي 3 بت ، كما هو واضح في دائرة Matrix1 العالمية في الشكل 11 ، تم تخطيها هنا من أجل الوضوح.

لا يمكن لمخرجات هذا السجل تشغيل العرض المكون من 7 مقاطع مباشرة لأن القيمة المخزنة هنا تتغير أثناء الفحص ويجب اعتبارها "صالحة" فقط في نهاية الفحص نفسه.

لهذا السبب ، تتصل مخرجات التسجيل المؤقتة بـ Matrix0's Loop Register عبر منافذ المصفوفة P13 و P14 و P15.

من المهم أن نلاحظ في الشكل 16 أن السجل المؤقت يتم تسجيله بواسطة خرج DCMP OUT + عندما يسجل ADC-SPI نتائج المقارنة بحد أقصى جديد تم العثور عليه.

يتم تمرير نفس إشارة OUT + إلى Matrix0 ، SPI CLK Logic ، عبر المنفذ P10.

الخطوة 12: تكوين الجهاز - خصائص مكونات Matrix1

توضح الأشكال 17-19 نوافذ خصائص المكونات التي تنتمي إلى Matrix1.

الخطوة 13: النتائج

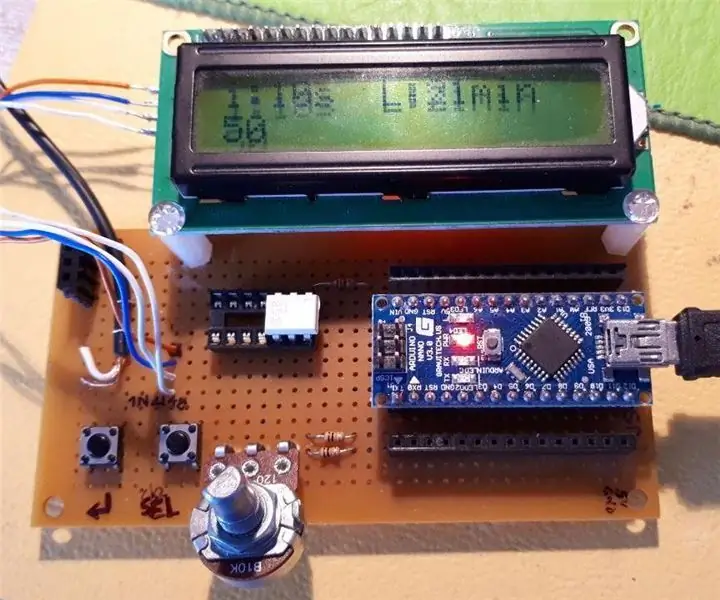

لاختبار التنفيذ ، تم إنشاء نموذج أولي للوحة التقييم ، حيث يتم الحصول على 8 جهد إدخال تناظري بواسطة سلسلة من فواصل المقاومة باستخدام TrimPots (كما هو موضح في الشكل 20).

معدد الإرسال المستخدم هو ADG508 ، وهو جزء يمكن أن يعمل بمصدر واحد (12 فولت).

برنامج تشغيل شاشة العرض المكون من 7 أجزاء هو 74LS47. يقوم بفك تشفير كلمة إدخال متوازية ويقود مباشرة عرض 7 مقاطع أنود مشترك.

تحتوي لوحة التقييم على موصل بزاوية قائمة 2 × 10 ليتم توصيله مباشرة بمنصة التطوير المتقدمة GreenPAK عند موصل التوسيع الخاص بها كما هو موضح في الشكل 21.

إن الاقتران مع GreenPAK Advanced Development Platform يجعل من السهل جدًا إجراء قياسات للإشارات لفحص سريع. على سبيل المثال ، يوضح الشكل 22 مجموعة من الإشارات (على التوالي CLOCK وإخراج ADC INT و DCMP OUT + الإخراج) كما تم التقاطها بواسطة HP 54620A Logic Analyzer. يتم تشغيل أشكال الموجة من خلال حافة صاعدة لإشارة OUT + (على النطاق المسمى "A> B") ، ومن ثم فإن هذا هو التقاط شكل موجة عندما يتم الكشف عن أقصى جهد جديد بين المدخلات التناظرية. في الواقع ، تم الحصول عليها عن طريق تدوير أحد TrimPots في لوحة التقييم لزيادة الجهد المقابل الموضح في الشكل 22.

يوضح الشكل 23 التخطيطي لمجلس التقييم.

استنتاج

في Instructable ، قمنا بتطبيق جهاز كشف الجهد الأقصى (أو الحد الأدنى) من ثماني قنوات لاستخدامه كإضافة شائعة لأنظمة التحكم متعددة القنوات. يستغل النهج المقدم الميزات المتقدمة لمكونات GreenPAK ويوضح كيف يمكن دمج الوظائف التناظرية والرقمية في شريحة واحدة. يمكن استبدال العديد من IC التجارية بـ Dialog GreenPAKs بحيث يمكن تقليل حجم التطبيق وتكلفته.

موصى به:

مقياس الجهد مع مقياس الجهد: 4 خطوات

Intervalometer with Potentiometer: لقد قررت فقط عمل مقياس فاصل بسيط للغاية ، مع مدخلات سهلة لمعلمات الفاصل الزمني. يستخدم مقياس الفترات زرين (Enter and Select) وزر جهد واحد (وعاء). باستخدام الأزرار ، يمكنك الدخول في وضع البرمجة أو s

مراقب الجهد لبطاريات الجهد العالي: 3 خطوات (بالصور)

مراقب الجهد لبطاريات الجهد العالي: سأشرح لك في هذا الدليل كيف صنعت جهاز مراقبة جهد البطارية للوح الطويل الكهربائي الخاص بي. قم بتركيبه بالطريقة التي تريدها وقم بتوصيل سلكين فقط بالبطارية (Gnd و Vcc). يفترض هذا الدليل أن جهد البطارية لديك يتجاوز 30 فولت ، ث

قراءة الجهد التناظري - أردوينو - كشف الكود # 1: 5 خطوات

قراءة الجهد التناظري - أردوينو - كشف الكود رقم 1: كشف الكود رقم 1 قراءة الفولت التناظري: يوضح لك هذا المثال كيفية قراءة إدخال تناظري على دبوس تناظري 0 ، وتحويل القيم من analogRead () إلى جهد ، وطباعته إلى المسلسل مراقبة برنامج Arduino (IDE)

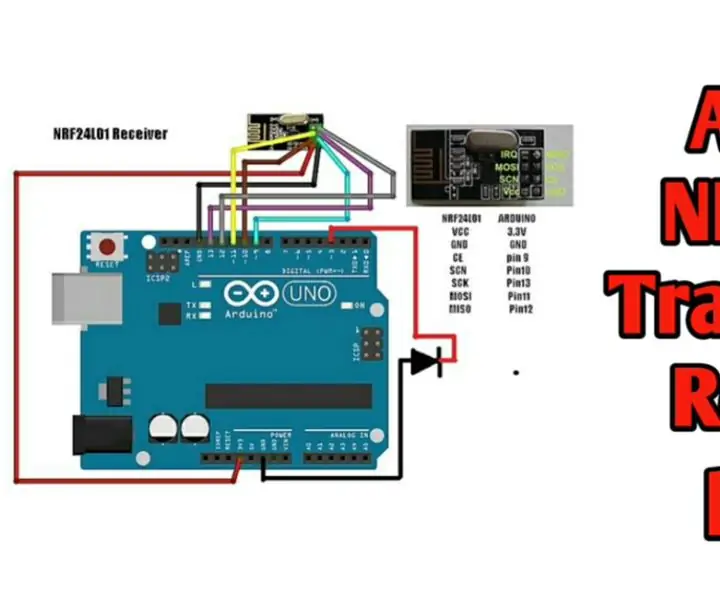

جهاز تحكم عن بعد لاسلكي باستخدام وحدة 2.4 جيجا هرتز NRF24L01 مع Arduino - جهاز استقبال Nrf24l01 4 قنوات / 6 قنوات للطائرة الرباعية - هليكوبتر ار سي - طائرة RC باستخدام Arduino: 5 خ

جهاز تحكم عن بعد لاسلكي باستخدام وحدة 2.4 جيجا هرتز NRF24L01 مع Arduino | جهاز استقبال Nrf24l01 4 قنوات / 6 قنوات للطائرة الرباعية | هليكوبتر ار سي | Rc Plane باستخدام Arduino: لتشغيل سيارة Rc | كوادكوبتر | طائرة بدون طيار | طائرة RC | قارب RC ، نحتاج دائمًا إلى جهاز استقبال وجهاز إرسال ، لنفترض بالنسبة لـ RC QUADCOPTER أننا بحاجة إلى جهاز إرسال واستقبال من 6 قنوات وأن هذا النوع من TX و RX مكلف للغاية ، لذلك سنصنع واحدًا على

توليد الجهد باستخدام دراجة مقياس الجهد: 9 خطوات (بالصور)

توليد الجهد باستخدام دراجة مقياس الجهد: تألفت صياغة المشروع من تجميع "لعبة" بهدف استخدام دواسة في دراجة مقياس سرعة موصولة بمولد وبرج من المصابيح التي يتم تنشيطها مع زيادة سرعة المحرك - وهو ما يتم منحه لـ الدراجة