جدول المحتويات:

- مؤلف John Day day@howwhatproduce.com.

- Public 2024-01-30 07:36.

- آخر تعديل 2025-01-23 12:53.

في الماضي ، قمت بكتابة دليل حول كيفية بناء جهاز كمبيوتر قائم على Z80 ، وقمت بتصميم الدائرة لتكون مبسطة قدر الإمكان بحيث يمكن بناؤها بأسهل ما يمكن. لقد كتبت برنامجًا صغيرًا أيضًا باستخدام نفس فكرة البساطة. نجح هذا التصميم إلى حد ما ، لكنني لم أكن سعيدًا به تمامًا. لقد بدأت بإعادة كتابة برنامج يسمح ببرمجته أثناء وقت التشغيل. كان هذا للسماح لي باختبار أجزاء من التعليمات البرمجية دون الحاجة إلى تكريسها لـ EEPROM ، والتي بدورها تتطلب مني إعادة برمجة EEPROM. لم تكن هذه فكرة ممتعة بالنسبة لي. ثم بدأت أفكر في مساحات الذاكرة. إذا كنت أرغب في واجهة جزء من الأجهزة (IO بشكل أساسي) ، فمن المحتمل أن يتجاوز جزء من الكود مقدار مساحة الذاكرة المتاحة للنظام. تذكر أن التصميم استخدم فقط البايت السفلي لناقل العنوان ثم تم استخدام البايت السفلي من البايت العالي للاختيار بين مساحات ROM وذاكرة الوصول العشوائي. هذا يعني أنه لم يكن لدي سوى 253 بايت من المساحة لاستخدامها. قد تسأل لماذا 253 بدلاً من 256. وذلك لأن شفري الجديد يضخ ثلاثة بايت من البيانات في نهاية برنامج مكتوب (سيتم تغطية هذا لاحقًا ، حيث قمت بتعديله للعمل على التصميم الجديد).

ن

عدت إلى مخططاتي القديمة لأرى ما يحدث أيضًا. لقد وجدت عيبًا صغيرًا في دائرة اختيار الذاكرة ، والتي سأغطيها عندما أصل إلى هناك. النسخة المبسطة: سيتم تنفيذ جميع طلبات الكتابة بالفعل ، على الرغم من وضعها دائمًا في ذاكرة الوصول العشوائي. ربما لم يكن هذا شيئًا يستحق القلق بشأنه ، لكنني أردت أن أفعل ذلك بشكل صحيح هذه المرة. وبهذا ، بدأت في رسم تخطيطي جديد. الصورتان المرفقتان بهذه الصفحة هما قبل الدائرة الفعلية وبعدها. لقد قمت بتنظيف الكثير من أسلاك السباغيتي ، هذا ليس مضحكا.

ن

إذا اتبعت مع رسالتي الأصلية وخططت للمتابعة مع هذا ، فسوف تكرهني. إذا كنت تبدأ من جديد ، فأنت محظوظ. ما عليك سوى الحصول على الأجزاء الموجودة في القائمة (أو ما يعادلها) والمتابعة.

اللوازم:

LM7805 - منظم 5 فولت Z80 - وحدة المعالجة المركزية ؛ أدمغة النظام AT28C64B - إيبروم. تخزين البيانات "الدائم" المستخدم للبرامج الثابتة للكمبيوتر IDT6116SA - SRAM ؛ تستخدم لتخزين رمز المستخدم و / أو تخزين البيانات العامة NE555 - ساعة النظام 74HC374 - Octal D-Latch with / OE ؛ تستخدم كرقاقة إدخال 74LS273 - Octal D-Latch with / MR ؛ رقاقة الإخراج TLC59211 - شريحة تشغيل LED (تُستخدم حتى تتمكن 74LS273 من تشغيل مصابيح LED ، حيث إنها وحدها غير قادرة على الإخراج الحالي) MC14572 - هذه شريحة "Line Driver" ، لكنني وجدت أنها مثالية لمنطق التحكم في الذاكرة. يحتوي على 4 محولات ، وبوابة NAND و NOR مدمجة 74LS32 - Quad OR gateCD4001 - Quad NOR gateCD4040 - 12 Stage Ripple Counter ؛ مقسم ساعة مرسومة ، لكن لم يتم تنفيذه (لتشغيل النظام بسرعات ساعة أبطأ) 2 10 كيلو أوم مقاومات - يتم استخدام أحدهما في دائرة المؤقت 555 ، لذا استخدم أي قيمة تريدها لـ it4 مقاومات 1 كيلو أوم - يتم استخدام واحد للمقاومات 555 دارة مؤقت ، لذا استخدم ما تريده. يتم استخدام آخر لقيادة مصابيح LED ، لذا قم بتنويعه أيضًا إذا كنت ترغب في 8x330 Ohm Resistor Bus8x10K Ohm Resistor Bus11 - يتم استخدام ثلاثة منها لحالة النظام والثمانية الأخرى عبارة عن نواتج. بالنسبة إلى 8 ، استخدمت عرض رسم بياني شريطي (HDSP-4836) 4 مكثفات - اثنان يستخدمان LM7805 ؛ 0.22 فائق التوهج و 0.1 فائق التوهج. إحداها لمؤقت 555 ، لذا استخدم ما تشعر أنه صحيح. الأخير هو إعادة التشغيل ؛ 100 فائق التوهج 2 نو أزرار الضغط - أحدهما يستخدم للإدخال ، والآخر لإعادة ضبط SPST DIP Switches - إدخال البيانات ؛ لقد استخدمت Piano Key styleWire. الكثير والكثير من الأسلاك

ن

ملاحظة: إصدار MC14572 عبر الفتحة قديم ، لكن إصدار SMD لا يزال نشطًا (ولا حتى حالة "ليس للتصميم الجديد") ، لذلك قد تحتاج إلى شراء لوحة دوائر للسماح لك باستخدامها. يمكن استخدام 74LS32 ثانٍ بدلاً من MC14572 (راجع مخطط "دائرة اختيار الذاكرة" للإصدار السابق)

الخطوة 1: نظرة عامة سريعة على التغييرات + المخططات

كيفية قراءة المخططات: السهم الذي يشير إلى شريحة هو أحد المدخلات: الإدخال> - السهم الموجه بعيدًا عن الشريحة هو ناتج: الإخراج <- تستخدم الحافلات خطًا بدلاً من السهم: ناقل | -

ن

تم رسم معظم الرقائق بمساميرها الدقيقة. وقد تم رسم الانخفاض البسيط على هذه الرقائق. تحتوي معظم الرقائق أيضًا على أرقام تعريف شخصية وتسميات عليها. قد يكون من الصعب قراءتها. كان قلمي مملًا.

ن

فيما يتعلق بتوصيلات الدوائر ، لم يتغير تصميم التصميم الجديد في الغالب عن التصميم الأصلي. لقد قمت بتوصيل الجزء السفلي من العنوان ذو البايت العالي بالذكريات ثم استخدمت الجزء المنخفض من nibble العلوي (A12) لاختيار ذاكرة الوصول العشوائي / ROM. هذا يعني أن مساحة ROM انتقلت من 0000-00FF إلى 0000-0FFF. انتقلت مساحة ذاكرة الوصول العشوائي من 0100-01FF إلى 1000-1FFF. لقد قمت أيضًا بتبديل منطق التحكم في الذاكرة للحصول على تصميم أفضل وأضفت مصباحين جديدين للحالة (وبعض منطق الغراء). لقد رسمت أيضًا (لكن لم أقم بسلك) دائرة مقسم ساعة. كان لأداء وظيفتين. الوظيفة الواضحة هي تقسيم تردد الساعة إلى أسفل. الوظيفة الأخرى هي لأغراض PWM (تعديل عرض النبض) ، حيث لا يولد 555 موجات مع دورات عمل بنسبة 50٪. هذا لا يهم حقًا في هذه الدائرة ، ولكن إذا كنت تريد استخدام الساعة لتشغيل بعض مصابيح LED ، فستلاحظ بالتأكيد التأثيرات (مجموعة (مجموعة) من مصابيح LED ستكون باهتة من الأخرى). باقي الدوائر بشكل أساسي لم تتغير.

الخطوة 2: وحدة المعالجة المركزية والذاكرة والتحكم في الذاكرة

هذا هو الجزء الذي يكرهني فيه قراء روايتي السابقة. في التصميم الأصلي ، ألقيت بعض الأجزاء على السبورة في مكان بدا وكأنهم سيفرضون مشكلة صغيرة في الحصول على الأسلاك. بدت النتيجة وكأن شخصًا ما ألقى طبقًا من السباغيتي عليه وكان مثل "الأسلاك!" كنت أرغب في تنظيفه قليلاً ، لذلك بدأت بتمزيق كل شيء باستثناء وحدة المعالجة المركزية وذاكرة الوصول العشوائي وذاكرة القراءة فقط. لقد سحبت ما يقرب من دائرة الإدخال بأكملها ودائرة الإخراج ومنطق الغراء. كاد أن أفعل ذلك يؤلمني ، لكنه كان ضروريًا. تركت جميع اتصالات البيانات سليمة والبايت السفلي لناقل العنوان. ثم قمت بعد ذلك بتوصيل الأجزاء الأربعة التالية من ناقل العنوان (A8-A11) بشريحة ROM. لقد حرصت على الالتفاف حول الشريحة هذه المرة لتسهيل سحبها لإعادة البرمجة. لقد قفزت أيضًا من اتصالات العناوين إلى شريحة ذاكرة الوصول العشوائي.

ن

مع ذلك بعيدًا ، كان عليّ الآن أن أحصل على منطق التحكم في الذاكرة. في المخطط الأصلي ، كنت قد قمت بتوصيل خط المعالج / MREQ مباشرة بـ / CE بكلا من شرائح الذاكرة ، ثم قمت بتوصيل / WR بذاكرة الوصول العشوائي / WE. ثم حصلت على وحدة المعالجة المركزية / RD و / MREQ منطقيًا أو كنت معًا بالإضافة إلى A9. بشكل أساسي ، تم إعداده بحيث يتم تنشيط جميع طلبات الذاكرة كلاً من ذاكرة الوصول العشوائي (RAM) وذاكرة القراءة فقط (ROM) ، ولكن تم استخدام A9 لتحديد أي من الرقائق / OE تم اختيارها. كان هذا جيدًا وكل ذلك لأن الرقائق ستظل غير نشطة حتى يتم تقديم طلب ذاكرة ، وعندئذٍ يكون واحد فقط / OE نشطًا أثناء طلب القراءة. منع هذا الحديث المتبادل ، لكنه أدخل فارقًا بسيطًا محرجًا. نظرًا لأنه تم استخدام A9 فقط لتحديد الشريحة التي تقوم بإخراج البيانات ولأن وحدة المعالجة المركزية لديها وصول مباشر إلى ذاكرة الوصول العشوائي / دبوس WE ، فإن أي وكل طلبات الكتابة ستمر. كان هذا جيدًا بالنسبة إلى ذاكرة القراءة فقط لأن وضع الكتابة الخاص بها تم تثبيطه عن طريق ربط / WE مباشرة بمصدر 5 فولت. ومع ذلك ، سيتم كتابة ذاكرة الوصول العشوائي بغض النظر عن A9. هذا يعني أن محاولة الكتابة إلى موقع مساحة ROM ستكتب إلى نفس الموقع في مساحة ذاكرة الوصول العشوائي.

ن

قد يكون أحد الحلول لذلك هو إعادة توصيل منطق التحكم بحيث تتمتع وحدة المعالجة المركزية بوصول مباشر إلى دبابيس الرقائق / OE و / WE ثم استخدام MREQ و A12 لتحديد الرقائق / CE التي تم تشغيلها. اتبعت هذه الفكرة ، ولكن بدلاً من استخدام أربعة بوابات NOR وعاكس مثل التصميم الأصلي ، وجدت شريحة صغيرة محرجة كانت مثالية للمهمة. اضطررت إلى إنشاء دائرة تستخدم فقط البوابات المنطقية المتوفرة في الشريحة ، لكن ذلك كان سهلاً بدرجة كافية. يتغذى A12 مباشرة في بوابة NAND وبوابة NOR. يتم إدخال / MREQ في بوابة NOR ويتم إدخال مجملها في بوابة NAND. تُستخدم بوابة NAND للقيادة / CE لذاكرة الوصول العشوائي (RAM) ويتم عكس إخراج NOR واستخدامه لقيادة ROM / CE. هذا يجعله / MREQ يجب أن يكون منخفضًا قبل تحديد أي من الشريحتين ثم يختار A12 أيهما يتم اختياره. مع هذا الإعداد ، الآن أي طلبات كتابة إلى ROM لن تفعل شيئًا. كما أنه يوفر الطاقة لأن شريحة واحدة فقط نشطة بدلاً من كليهما. أما بالنسبة للرقاقة المنطقية نفسها ، فلا يزال لدينا عاكسان غير مستخدمين بالداخل. سوف يعتاد المرء لاحقًا ، لكننا سنصل إلى هناك عندما نصل إلى هناك.

الخطوة 3: مؤشرات LED لحالة النظام

قبل أن أبدأ هذا المشروع ، كنت أحاول التفاعل مع IC معين ، لكنني كنت أواجه مشكلة في ذلك. غير متأكد مما كان يحدث ، لقد استخدمت مصباح LED مثبت على اللوحة للتحقيق حول (أحد تلك التجميعات التي تحتوي على مقاوم مدمج). أعطاني القيام بذلك فكرة حنين لا تزال مستخدمة حتى اليوم: تستخدم مصابيح LED الخاصة بالحالة للإشارة إلى ما إذا كانت الذاكرة تتم قراءتها أو الكتابة إليها. كان من المقرر استخدامه بالاقتران مع مدخلات LED لدي بالفعل. تم توصيل مؤشر LED للإدخال بمولد إشارة / WAIT ليوضح لنا أن النظام ، حسنًا ، ينتظر الإدخال (سأصل إلى هناك ، لا تقلق). لقد فكرت في إضافة مؤشر LED للإشارة إلى كتابة IO ، لكنني اعتقدت أن تغيير مصابيح LED للإخراج سيكون بالفعل مؤشرًا رائعًا على ذلك. بالتفكير في الأمر ، لا يزال بإمكاني إضافته حتى الآن. ومع ذلك ، أجد أنه من المفيد معرفة ما إذا كانت الذاكرة تُقرأ أو تُكتب. حسنًا ، إنه مفيد لتصحيح أخطاء البرنامج على أي حال. لقد استفدت منه كثيرًا على هذا النحو عند محاولة تشغيل برنامجي: "لماذا يكتب في الذاكرة؟ ليس من المفترض أن تفعل ذلك بعد!"

ن

للتحكم في هذه المصابيح ، استخدمت بوابة NOR الرباعية. لقد استخدمت كل البوابات. تم استخدام اثنين فقط لتوليد إشارات الحالة ، لكن الشريحة لا تمتلك إمكانيات الطاقة لتشغيل مصابيح LED بالفعل. إنهم قادرون على غرق هذا القدر من الطاقة ، لذلك استخدمت بوابتي NOR الأخريين كمحولات وربطت المصابيح على هذا النحو. نظرًا لاستخدام أحد LED للإشارة إلى القراءات والآخر للكتابة ، ولن يحدث طلب القراءة والكتابة في نفس الوقت ، فقد تمكنت من استخدام مقاوم واحد فقط لكل من مصابيح LED. بالنسبة للإشارات التي أحتاجها لفك تشفيرها ، كان ذلك سهلاً أيضًا. كنت أرغب في الإشارة إلى جميع طلبات قراءة الذاكرة ، لذلك كانت بوابة NOR الأولى / MREQ و / RD على مدخلاتها. كانت حالة الكتابة أصعب قليلاً ، لكنها كانت سهلة. ما زلت أستخدم / MREQ كمدخل واحد ، لكن استخدام / WR مثل الآخر قد يتسبب في فارق بسيط كنت أرغب في تجنبه. كان سيشير إلى جميع طلبات الكتابة. أردت فقط تلك التي مرت بالفعل. فكيف أفعل ذلك؟ حسنًا ، تذكر كيف لديّ إعداد النظام بحيث لا يمكن كتابة سوى ذاكرة الوصول العشوائي؟ لقد استخدمت RAMs / CE كمدخل آخر لبوابة NOR. هذا يعني أن مؤشر LED سيضيء فقط عند تحديد ذاكرة الوصول العشوائي وإجراء طلب كتابة. من حيث لون LED ، اخترت اللون البرتقالي كمؤشر للقراءة (لكنني وجدت اللون الأصفر فقط) والأحمر كمؤشر للكتابة.

الخطوة 4: الإدخال والإخراج

في الخطوة السابقة ، ربما لاحظت أنني أضفت بعض المكونات المتبقية إلى اللوحة بالفعل. كنت أقوم بحجز المساحة حتى لا أضع الأسلاك عن طريق الخطأ حيث أردت مكونًا (وبالتالي يجب أن أجد موقعًا جديدًا للمكون المذكور). ربما لاحظت أيضًا أنني تركت مفاتيح الإدخال في مكانها وتم توصيلها بسكة الطاقة. قررت أن الموقع الأصلي كان المكان المثالي وقررت وضع مصابيح LED للإخراج في مكان قريب (أعلاه). على يمين شاشة الشريط يوجد مزلاج الإدخال. وفوق ذلك يوجد مزلاج الإخراج ، وعلى يساره يوجد مشغل LED. لقد بدأت بتوصيل الشاشة بالسائق لأن ذلك كان أسهل ما يمكن القيام به. ثم قمت بتوصيل المفاتيح إلى جانب الإدخال من مزلاج الإدخال. بعد ذلك ، قمت بتوصيل جانب الإخراج من مزلاج الإخراج بمحرك LED. قد يبدو هذا وكأنه أمر محرج لتوصيل هذه الأسلاك ، لكن ذلك كان لسبب ما. كان من المقرر توصيل مدخل مزلاج الإخراج بحافلة البيانات بالإضافة إلى إخراج مزلاج الإدخال. كانت الفكرة هي توصيل مخرجات مزلاج الإدخال بمدخلات مزلاج الإخراج ، وهو ما فعلته. ثم كل ما كان علي فعله هو توصيل هذه الفوضى بحافلة البيانات. لا يهم أين ذهبت هذه الوصلات فعليًا لأنها ستكون جميعها متصلة كهربائيًا. الكمبيوتر الآن على وشك الانتهاء.

الخطوة 5: إعادة تعيين وإنهاء الإدخال والإخراج

آسف ، لا توجد صور لهذه الخطوة. الرجوع إلى الخطوة السابقة للصور.

ن

ربما لاحظت في آخر صورة من الخطوة السابقة ، كان لدي زر أخضر وشريحة منطقية أخرى مثبتة. الرقاقة هي بوابة OR. يتم استخدام بوابتين لتوليد إشارة / WAIT. حسنًا ، يولد المرء الإشارة بواسطة OR-ing / IORQ و / RD من المعالج. يتم إدخال الإخراج في البوابة الثانية ، حيث يتم إدخال "أو" مرة أخرى إلى زر ضغط. يقوم الزر بجلب مدخلات البوابة عالية ، وبالتالي رفع مستوى المخرجات. يتم تغذية هذا الإخراج إلى المعالجات / دبوس الانتظار. أثناء عدم الضغط عليه ، يحافظ المقاوم على الإدخال منخفضًا. لقد استخدمت مبدئيًا مقاومًا بقوة 10 كيلو بايت ، لكن LS32 كان يعمل في الواقع على إخراج الجهد من المدخلات. المقاوم لم يسقطه منخفضًا بدرجة كافية واضطررت إلى استبداله بـ 1K. على أي حال ، الفكرة هي أنه عند إجراء طلب قراءة IO ، فإن بوابات OR الأولى والثانية تخبر المعالج بالانتظار. بمجرد ضبط مفاتيح الإدخال على ما تريد ، تضغط على الزر ويخرج وحدة المعالجة المركزية من حالة الانتظار. إن مؤشر LED "المدخل" الأخضر ، كما سميته في خطوة سابقة ، يكون سلكيًا بحيث يضيء عندما ينخفض دبوس / WAIT.

ن

لكننا لم ننتهي بعد. يحتاج فليب الإدخال إلى إشارة لإعلامه عندما يكون إدخال البيانات صالحًا ويجب إخراجه في وحدة المعالجة المركزية. دبوس الساعة هذا نشط بدرجة عالية. من قبل ، قمنا فقط بتوصيله بالزر. لا يزال هذا خيارًا صالحًا ، لكن هذه المرة اخترت وضعه على نفس الإخراج مثل بوابة OR الثانية. يحتوي هذا IC أيضًا على دبوس / OE يحتاج إلى دفعه. إذا كان سيتم رفعه ، فلن يقوم بإدراج البيانات في الحافلة أبدًا. إذا تم الإبقاء عليه منخفضًا ، فسيكون دائمًا يقود الحافلة. لإصلاح ذلك ، استخدمت ببساطة بوابة OR ثالثة. المدخلات هي / IORQ و / RD ويذهب الإخراج مباشرة إلى المزلاج / OE.

ن

يحتاج مزلاج الإخراج أيضًا إلى أن يتم تشغيل دبوس الساعة. مرة أخرى ، هو نشط مرتفع. في التخطيطي الخاص بي ، قمت برسم البوابة الرابعة أو التي تقود الدبوس مباشرةً باستخدام / IORQ و / WR. هذا يعني أن دبوس الساعة سيظل مرتفعًا حتى يتم تقديم طلب الكتابة ، ثم ينخفض ثم يرتفع مرة أخرى. من المحتمل أن يكون هذا جيدًا لأن ناقل البيانات كان سيظل يحتوي على بيانات صالحة عليه مباشرة بعد محاولة الكتابة ، ولكن من وجهة نظر هندسية ، كان تصميمًا غير حقيقي. لم ألاحظ هذا الخطأ إلا بعد أن التقطت الصور النهائية ، لكنني قمت بتمزيق هذا الاتصال ثم قمت بتغذية مخرج بوابة OR في أحد المحولات غير المستخدمة من منطق التحكم في الذاكرة ، ثم قمت بتوصيل مخرجاته بدبوس الساعة. لقد أصلحت أيضًا التخطيطي ووجدت خطأ آخر قمت به. انا صححتها ايضا

ن

بعد الانتهاء من كل ذلك أخيرًا ، كان لدي قدر ضئيل جدًا من العمل للقيام به: إعادة تعيين الدائرة. أضفت زرًا إلى اللوحة واستخدمت مقاومًا بقوة 10 كيلو بايت لرفع جانب واحد. يذهب الجانب الآخر مباشرة إلى الأرض. الجانب الذي تم رفعه هو إخراج / RESET ، والذي ذهب إلى كل شريحة باستخدام / RESET pin (وحدة المعالجة المركزية ومزلاج الإخراج). لإنجاز إعادة تشغيل الطاقة ، أضفت مكثفًا إلى خرج / إعادة الضبط. الفكرة هي أن المقاوم ذو القيمة الكبيرة من شأنه أن يتسبب في شحن المكثف الكبير نسبيًا ببطء مع إبقاء دبابيس / RESET منخفضة لبعض دورات الساعة (تحتاج وحدة المعالجة المركزية إلى أربع دورات على مدار الساعة). ربما يمكنك بالفعل تخمين الجانب السلبي من هذه الدائرة. إنها نفس النسخة السلبية من الإصدار السابق لأنها نفس الدائرة. عندما يتم الضغط على الزر ، يتم اختصار المكثف بشكل أساسي خلال الزر. يعد هذا أمرًا سيئًا لكل من الغطاء والزر ، لذلك إذا كنت ترغب في جعل التصميم الخاص بك أكثر ديمومة ، فقد ترغب في إعادة تصميمه. كنت أفكر في مؤقت 555 آخر تم إعداده في وضع monostable. ولكن مع ذلك ، انتهت دائرة الكمبيوتر الآن. ياي. الآن يحتاج مبرمج.

الخطوة السادسة: البرمجة

كانت برمجة هذا الشيء بمثابة كابوس. لقد قمت ببناء مبرمج Arduino EEPROM. لم تنجح. لقد أنشأت واحدة أخرى بناءً على تصميم وترميز شخص آخر. ما زلت لا تعمل. عدت إلى الطريقة المجربة والصحيحة لإعداد العناوين والبيانات يدويًا يدويًا. بطريقة ما ، أفسدت ذلك. حاولت مرة أخرى وما زلت أخطأت. عدت مرة أخرى واكتشفت أنه تم إيقافه بمقدار بايت واحد ، لذلك قمت بتصحيحه ونجح أخيرًا ، والحمد لله.

ن

بالنسبة للبرنامج الفعلي ، يبدو أنه معقد للغاية ويصعب متابعته ، لكنه ليس كذلك. الأمر بسيط للغاية في الواقع. نصفه ينسخ الأرقام من حوله. يتم مشاركة النصف الآخر بين الرياضيات ذات 16 بت ، والقفزات الشرطية ، وحتى المزيد من نسخ الأرقام حولها. لذا اسمحوا لي أن أتصفحها وأخبرك كيف تعمل.

ن

التهيئة تحدد فقط بعض قيم التسجيل ليستخدمها البرنامج. حلقة البرنامج أكثر تعقيدًا بعض الشيء ، ولكنها ليست كاملة. أولاً ، يقبل الإدخال إلى السجل A على المنفذ 00. ثم يتم كتابة السجل E في الذاكرة. في الحلقتين الأوليين ، يحتوي السجل E على بيانات غير مهمة ، لذلك نحاول كتابتها إلى آخر وحدتي بايت من مساحة ROM لأنه لن يتم كتابتها بالفعل ؛ ثم تتم زيادة مؤشر العنوان (IY). ثم يتم نقل القيمة المخزنة في D إلى E ليتم كتابتها بعد ذلك. ثم يتم تحميل A إلى D و L و E يتم نسخها إلى H. HL حيث تتم مقارنة القيمة عن طريق الطرح والتحقق من ZF (علامة صفرية). يتم تخزين القيمة الأولى التي تمت مقارنتها مقابل في السجلات B و C. يتم التعامل مع B و C كسجل واحد من 16 بت ، BC. إذا كانت القيم هي نفسها ، فإن البرنامج ينتقل مباشرة إلى مساحة ذاكرة الوصول العشوائي ، حيث يفترض أن يتواجد رمز المستخدم. إذا لم يكن الرمز في BC غير مطابق ، فسيتم إعادة تحميل HL بالقيم الأولية من D و E والمقارنة مرة أخرى بالقيمة في SP بنفس الطريقة التي تمت مقارنتها بـ BC. إذا كانت مطابقة ، فسيكون لها نفس النتيجة ، ولكن تتم كتابة ثلاثة بايتات إضافية في الذاكرة. البايت هي رمز يتسبب في عودة وحدة المعالجة المركزية إلى بداية برنامجها (إعادة تعيين البرنامج). ومع ذلك ، إذا لم تكن المقارنة الثانية مطابقة ، فسيقوم البرنامج بالتكرار إلى حيث يحصل على قيمة من المستخدم.

ن

LD SP ، EDBFH ؛ كود exe (يضيف قفزة)

ن

LD IY، FFEH؛ مؤشر الذاكرة الأولية لتخزين التعليمات البرمجية

ن

LD BC ، EDC3H ؛ كود exe (بدون حلقة)

ن

حلقة ؛ توجيه المجمّع حتى لا نضطر إلى معرفة مكان وجود هذا الجزء في الذاكرة

ن

في أ ، (00 ح) ؛ الحصول على بيانات البرنامج

ن

LD (IY + 00H)، E ؛ يحتوي E على رمز ليتم تخزينه

ن

INC IY ؛ الانتقال إلى موقع الذاكرة التالي

ن

LD E ، D ؛ ld D إلى E.

ن

LD D ، A ؛ من أ إلى د

ن

LD H ، E ؛ ld E إلى H.

ن

LD L ، D ؛ ld D إلى L.

ن

أو أ ؛ إعادة تعيين علم الحمل

ن

SBC HL ، BC ؛ تُرجع 0 إذا تم إدخال كود exe 2

ن

JP Z ، 1000H ؛ إذا كان الأمر كذلك ، فانتقل إلى البرنامج ونفذه

ن

LD H ، E ؛ وإلا ، قم بتحديثها إلى القيم المناسبة

ن

LD L، D

ن

أو أ ؛ قد يكون طرح أول علامة حمل. مسحها

ن

SBC HL ، SP ؛ إرجاع 0 إذا تم إدخال رمز exe 1

ن

JP NZ ، حلقة ؛ إذا لم يكن كذلك ، كرر العملية (بدءًا من الحصول على قيمة)

ن

LD (IY + 00H) ، C3H ؛ وإلا ، فقم بإدخال رمز قفزة في نهاية برنامج المستخدم

ن

LD (IY + 01H) ، 00H ؛ القفز بمثابة إعادة تعيين البرامج

ن

LD (IY + 02H) ، 00H ؛ إنها إعادة تعيين كاملة في حالة تعديل السجلات

ن

JP 1000H ؛ الانتقال إلى برنامج المستخدم وتنفيذه

موصى به:

تجاوز المعايير القياسية - إعادة النظر: 5 خطوات

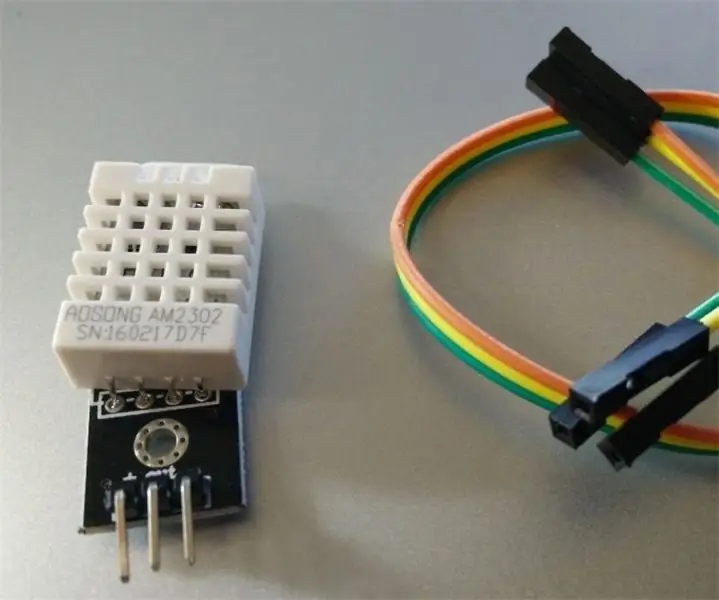

الذهاب إلى ما وراء StandardFirmata - تمت إعادة النظر فيه: منذ فترة وجيزة ، اتصل بي الدكتور Martyn Wheeler ، مستخدم pymata4 ، للحصول على إرشادات حول إضافة دعم لمستشعر الرطوبة / درجة الحرارة DHT22 إلى مكتبة pymata4. مكتبة pymata4 ، جنبًا إلى جنب مع نظيرتها في Arduino ، FirmataExpre

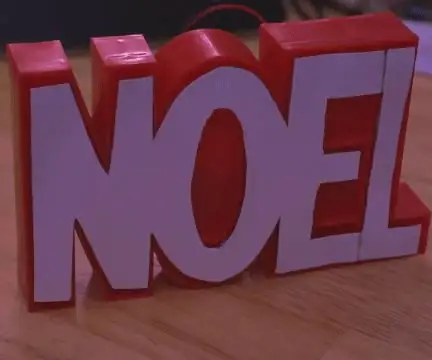

إعادة استخدام زينة عيد الميلاد LED القديمة عن طريق إعادة مزجها: 7 خطوات

إعادة استخدام زينة عيد الميلاد LED القديمة عن طريق إعادة مزجها: لقد اشتريت زينة عيد الميلاد البشعة إلى حد ما في متجر باوند (أي متجر بالدولار) خلال مبيعات ما بعد الموسم قبل ثلاث سنوات. لقد كان & quot؛ NOEL & quot؛ مخيبًا علامة مضاءة بعدد غير كافٍ من مصابيح LED التي تعمل بالبطارية

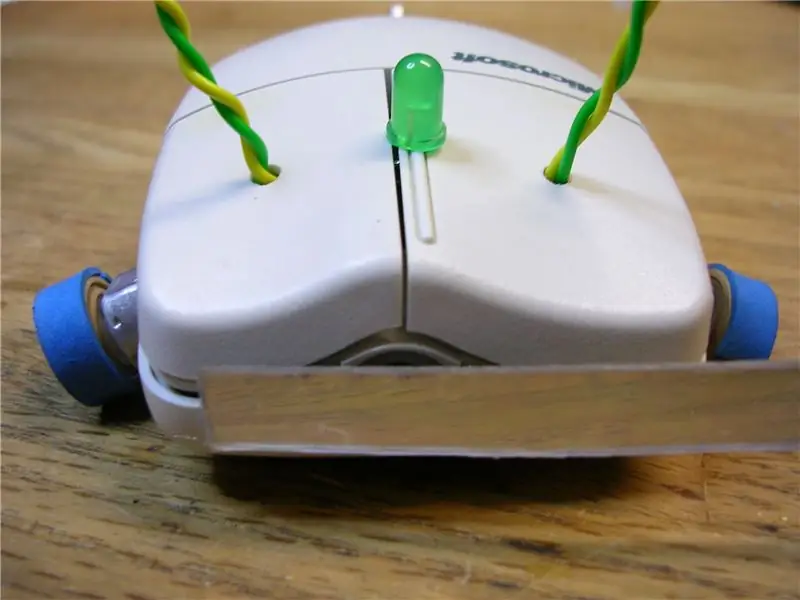

إعادة النظر في Mousebot: 10 خطوات (بالصور)

Mousebot Revisited: Mousebot من Make vol 2 هي مقدمة ممتعة للروبوتات. ممتع للغاية لدرجة أنني قمت بإنشاء هذه الوثائق الموسعة لبناء Mousey من البداية إلى النهاية ، مع بعض النصائح الإضافية القليلة التي لن تجدها في mag. أفضل طريقة لفهم هذه الطريقة بعد

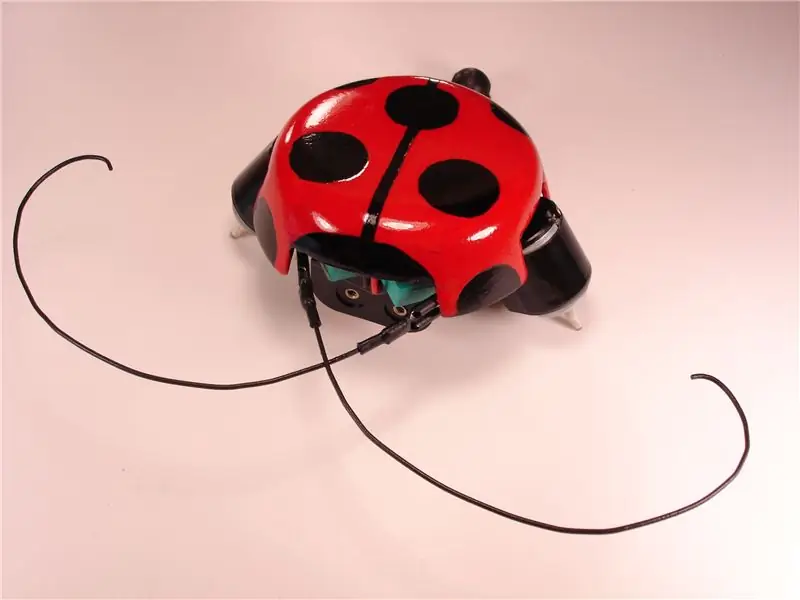

كيفية بناء روبوت - BeetleBot V2 (تمت إعادة النظر فيه): 23 خطوة (بالصور)

كيفية بناء روبوت - BeetleBot V2 (تمت إعادة النظر فيه): هذا هو روبوت الخنفساء الذي أعيد النظر فيه بأسلوب MythBusters! لقد صنعت في الأصل تعليمات حول الإصدار 1. لقد حان الوقت الآن لعرض نسخة جديدة من هذا الروبوت الرائع. هذا الإصدار الجديد أسهل بكثير في إنشاء

موسع نطاق WIFI أحادي الاتجاه - تمت إعادة النظر فيه: 3 خطوات

موسع نطاق WIFI أحادي الاتجاه - تمت إعادة النظر فيه: الخطوة الأولى - انتقل إلى هذا الرابط: (ثم عد هنا) https://www.instructables.com/id/Uni-Directional-WIFI-Range-Extender/؟ALLSTEPS"؛tm36usa"؛ نشرت هذا في يوليو 2006. أخيرًا تمكنت من صنع واحدة في أبريل 2009 لأنني أقوم بالكثير من العمل