جدول المحتويات:

- الخطوة 1: قم بتكوين Zynq Programmable Logic for Transmitter

- الخطوة 2: قم بتكوين Zynq Programmable Logic for Receiver

- الخطوة 3: إعداد برنامج تشغيل VDMA

- الخطوة 4: إعداد شبكة Nanorouter

- الخطوة 5: إعداد نظام معالجة Zynq لنقل البيانات عبر إيثرنت

- الخطوة 6: إعداد نظام معالجة Zynq لاستقبال البيانات عبر إيثرنت

- الخطوة 7: قم بتوصيل Zybo Boards بمصدر HDMI و HDMI Sink

- الخطوة 8: أفكار بديلة للتحسين

- الخطوة 9: إمكانية الوصول

- مؤلف John Day [email protected].

- Public 2024-01-30 07:40.

- آخر تعديل 2025-01-23 12:54.

هل تمنيت يومًا أن تتمكن من توصيل تلفزيونك بجهاز كمبيوتر شخصي أو كمبيوتر محمول كشاشة خارجية ، ولكنك لا تريد أن يكون لديك كل تلك الأسلاك المزعجة في الطريق؟ إذا كان الأمر كذلك ، فهذا البرنامج التعليمي مخصص لك فقط! في حين أن هناك بعض المنتجات التي تحقق هذا الهدف ، فإن مشروع DIY يكون أكثر إرضاءًا وربما أرخص.

يختلف هذا المفهوم عن منتجات مثل chromecast ، حيث إنه يهدف إلى أن يحل محل سلك HDMI المتصل بشاشة بدلاً من أن يكون جهاز بث.

تم إنشاء مشروعنا كمشروع نهائي لدورة أنظمة تشغيل الوقت الحقيقي في جامعة ولاية كاليفورنيا للفنون التطبيقية ، سان لويس أوبيسبو.

الهدف من المشروع هو استخدام لوحتين Digilent Zybo لتعملوا كواجهة اتصال لاسلكي بين جهاز إرسال HDMI (كمبيوتر شخصي ، بلو راي ، إلخ) إلى جهاز استقبال HDMI (شاشة سطح المكتب ، جهاز عرض ، تلفزيون ، إلخ).

سيتم توصيل One Digilent Zybo عبر HDMI بجهاز الإرسال ، وسيتم توصيل الآخر عبر HDMI بجهاز الاستقبال.

سيتم إجراء الاتصال اللاسلكي باستخدام شبكة محلية لاسلكية مخصصة لجهاز الإرسال والاستقبال ، دون أن يتم توجيهها عبر جهاز توجيه منزلي أو جهاز آخر من هذا القبيل. الوحدة اللاسلكية المستخدمة لهذا المشروع هي tplink wr802n nanorouter ، يعمل أحدهما كنقطة وصول لإنشاء الشبكة والآخر يعمل كعميل للاتصال بالشبكة. سيتم توصيل كل جهاز توجيه نانوي عبر كابل إيثرنت بأي من لوحة Zybo. عند الاتصال بأجهزة التوجيه هذه ، ستتواصل الأجهزة عبر TCP كما لو كانت متصلة بكابل إيثرنت واحد (بمعنى أن التكوين الوحيد المطلوب لإنشاء اتصال هو عنوان IP الخاص بالعميل).

بينما كان الهدف من المشروع هو تسهيل دفق فيديو 1080x720 @ 60Hz ، لم يكن ذلك قابلاً للتحقيق بسبب قيود النطاق الترددي في الشبكة اللاسلكية ونقص ضغط الفيديو في الوقت الفعلي لتقليل البيانات المطلوبة للإرسال. بدلاً من ذلك ، يعمل هذا المشروع كإطار عمل للتطوير المستقبلي لتحقيق هذا الهدف ، حيث أنه قيد بشدة القيود في معدل الإطارات لدفق بيانات HDMI بشكل صحيح على النحو المنشود.

متطلبات المشروع:

2x Digilent Zybo Development Boards (يجب أن يكون لديك منفذ HDMI واحد على الأقل)

عدد 2 كبلات HDMI

كبلات 2x microusb (لتوصيل Zybo بجهاز الكمبيوتر من أجل التطوير)

2x tplink wr802n nanorouters (بما في ذلك محولات الطاقة adtl. 2x microusb ومأخذ الطاقة بالحائط)

2x كابل إيثرنت

*** ملاحظة: يفترض هذا البرنامج التعليمي الإلمام بمجموعة تصميم Vivado وتجربة إنشاء مشروع جديد وتصميم الكتلة. ***

الخطوة 1: قم بتكوين Zynq Programmable Logic for Transmitter

كان نهجنا في تطوير المنطق القابل للبرمجة لجهاز الإرسال هو إجراء تمرير hdmi إلى hdmi من جهاز الكمبيوتر للمراقبة باستخدام كتلتين للوصول المباشر للذاكرة (VDMA) ، أحدهما للكتابة والآخر للقراءة.

تم تحديد كلاهما للتشغيل الحر ، وضع المخزن المؤقت للإطارات 3 (0-1-2). نظرًا لأنه تم تحسين قلب الفيديو لـ 60 إطارًا في الثانية ، فهذا يعني أن VDMA سيكتب أو يقرأ إلى إطار جديد كل 16.67 مللي ثانية بهذا الترتيب: 0 ، 1 ، 2 ، 0 ، 1 ، 2 ، 0 ، 1 ، 2. تختلف مواقع ذاكرة DDR لكل إطار بالنسبة إلى VDMAs لأنها لم تعد متزامنة مع بعضها البعض. بدلاً من ذلك ، يتم استخدام مؤقت الأجهزة (TTC1) ، الذي تم تكوينه لـ 60 هرتز ، لمزامنة حركة البيانات بين موقعي الذاكرة.

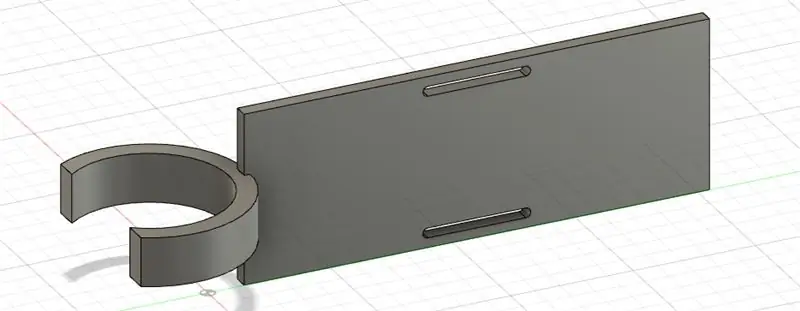

تُظهر الصورة أعلاه 3 إطارات وأبعادها ومقدار الذاكرة التي يتطلبها كل منها (على يمين الإطار). إذا قمنا بتعيين VDMA للكتابة إلى مواقع الذاكرة هذه ، فيمكننا تعيين مواقع ذاكرة VDMA للقراءة خارج هذه المجموعة ، على سبيل المثال بدءًا من 0x0B000000. يتكون كل إطار من 1280 * 720 بكسل وكل بكسل يتكون من 8 بتات من الأحمر والأخضر والأزرق بإجمالي 24 بت. هذا يعني أن الإطار يتكون من 1280 * 720 * 3 بايت (2.76 ميجابايت).

داخل جهاز ضبط الوقت IRQ ، الموضح في إعداد برنامج تشغيل VDMA ، سوف يتعامل مع نسخ البيانات بين موقعي ذاكرة VMDA. يوفر VDMA مؤشرًا للإطار الحالي الذي تتم الكتابة إليه أو القراءة منه. يتم تمثيل الإطار برمز رمادي معين ، والذي يتم تحويله في البرنامج. يمكن العثور على تعريفات الكود الرمادية لتكوين المخزن المؤقت للإطارات 3 في دليل منتج AXI VDMA في الملحق ج.

هذا يسمح لنا بنسخ المحتويات التي يتم كتابتها إلى الذاكرة دون القراءة من إطار تتم الكتابة إليه حاليًا.

*** لاحظ أنه لا يتم استخدام قراءة VDMA عند إرسال البيانات عبر الشبكة اللاسلكية. الغرض فقط هو التحقق من التشغيل الصحيح لنسخ الذاكرة من الكتابة VMDA. يجب تعطيل VMDA للقراءة. ***

فيما يلي خطوات إنشاء كتلة تصميم جهاز الإرسال:

- عند إنشاء مشروع جديد ، من الجيد تخصيص شريحة أو لوحة للمشروع. يصف هذا الرابط كيفية إضافة ملفات لوحة جديدة إلى دليل Vivado وربط اللوحة الصحيحة بمشروعك. سيكون مفيدًا عند إضافة كتلة نظام المعالجة والانتقال من الأجهزة إلى البرامج (جانب SDK).

-

أضف الكتل التالية:

- dvi2rgb

- دخل الفيديو إلى Axi4-stream

- تحكم التوقيت

- axi4 تيار إلى vid

- rgb2dvi

- AXI VDMA x2.0

- AXI GPIO x2.0

- معالج الساعة

- ثابت

- نظام المعالجة Zynq

- عند إضافة نظام المعالجة ، انقر فوق "تشغيل بلوك التشغيل الآلي" من الشريط الملون الأخضر العلوي وتأكد من تحديد الخيار "تطبيق الإعداد المسبق للوحة". اترك كل شيء آخر افتراضيًا.

- يمكن العثور على صور كل نافذة تكوين كتلة في الصور أعلاه. إذا كنت لا ترى صورة لنافذة معينة ، فقط اتركها كإعداد افتراضي.

-

ابدأ في تكوين نظام المعالجة Zynq:

- في تكوين PS-PL ، قم بتمكين AXI Non Secure ، قم بتمكين GP Master AXI ، قم بتمكين واجهة M AXI GP0

- في واجهة HP Slave AXI لتكوين PS-PL ، قم بتمكين كل من HP0 و HP1

- في تكوين MIO تأكد من تمكين ENET0 ضمن I / O Peripherals ، ثم Application Processor Unit ، قم بتمكين Timer0

- في Clock Configuration PL Fabric Clocks ، قم بتمكين FCLK_CLK0 واضبطه على 100 ميجا هرتز.

- انقر فوق موافق

- قبل النقر على "تشغيل أتمتة الاتصال" ، تأكد من توصيل مقاطع الفيديو كما هو موضح في صورة تصميم قالب TX أعلاه. سترغب في إعادة تسمية الثابت إلى VDD وتعيين القيمة على 1. قم بتوصيل كتل الفيديو وفقًا لذلك.

- اجعل ساعة HDMI TMDS ودبابيس البيانات خارجية على كتل rgb2dvi و dvi2rgb

- قم بإنشاء منفذ إدخال وإخراج لإشارة الكشف عن المكونات الساخنة (HPD) وقم بتوصيلها معًا ، وهي محددة في ملف القيود

-

يتم استرداد ساعة البكسل من TMDS_Clk_p ، والتي تم إنشاؤها في ملف القيود. سيكون هذا 74.25 ميجا هرتز وفقًا لدقة 720 بكسل. من المهم توصيل ساعة البكسل (من كتلة dvi2rgb) بالدبابيس التالية:

- vid_io_in_clk (vid في كتلة تيار أكسي)

- vid_io_out_clk (تيار محوري إلى كتلة vid out)

- clk (جهاز التحكم في التوقيت)

- PixelClk (rgb2dvi)

- *** ملاحظة: حاليًا ، لتنشيط استرداد ساعة البكسل ، يجب توصيل موصلات HDMI rx و tx بمصدر / حوض نشط. إحدى الطرق للتغلب على ذلك هي فصل مقاطع الفيديو rx و tx إلى مجالات ساعة مختلفة (بمعنى آخر ، إنشاء ساعة جديدة 74.25 ميغاهرتز لتغذية كتلة tx). ***

- قم بعد ذلك بإعداد معالج الساعة بحيث يكون لديك إدخال 100 ميجاهرتز (مصدر المخزن المؤقت العالمي) و 3 ساعات إخراج عند 50 ميجاهرتز (ساعة AXI-Lite) ، و 150 ميجاهرتز (ساعة AXI4-Stream) ، و 200 ميجاهرتز (dvi2rgb RefClk pin).

- قم بتوصيل دبوس نظام المعالجة FCLK_CLK0 بإدخال معالج الساعة

- عند هذه النقطة ، انقر فوق "تشغيل أتمتة الاتصال" من الشريط الأخضر أعلى نافذة التصميم. من المستحسن القيام بذلك لكتلة واحدة في كل مرة واتباع صورة تصميم قالب TX أعلاه.

- ستحاول الأداة إضافة AXI Interconnect ، والذي يعمل بمثابة رابط رئيسي / تابع للكتل التي تستخدم ناقل AXI-Lite (VDMAs و GPIOs).

- ستضيف أيضًا AXI SmartConnect ، الذي يعمل كوصلة رئيسية / تابعة لواجهات معالج AXI4-Stream و High Performance المستخدمة بواسطة VDMA (دفق إلى خريطة الذاكرة والعكس بالعكس).

- ستضيف الأداة أيضًا إعادة تعيين نظام المعالج. تأكد من أن هذا متصل فقط بـ VDMAs و GPIOs والكتل ذات الصلة بالمعالج. لا تقم بتوصيله بأي كتل فيديو (على سبيل المثال ، dvi2rgb ، جهاز التحكم في التوقيت ، vid للتدفق وما إلى ذلك)

- بمجرد اكتمال أتمتة الاتصال ، تحقق من تطابق الاتصالات مع صورة تصميم كتلة الإرسال. ستلاحظ وجود كتلة إضافية لـ System ILA لم يتم ذكرها. هذا من أجل التصحيح فقط وليس هناك حاجة في الوقت الحالي. يستخدم معالج 150M Processor Reset ، لذلك لا داعي لذلك أيضًا. في أي مكان ترى فيه "حشرات" خضراء صغيرة على الحافلات ، يكون ذلك بسبب قانون إدارة الأراضي ويمكن تجاهله.

- الخطوة الأخيرة هي النقر بزر الماوس الأيمن على تصميم الكتلة في شجرة مصادر المشروع وتحديد "إنشاء غلاف HDL". إذا كنت تخطط لإضافة منطق إلى الغلاف ، فسيتم الكتابة فوقه في كل مرة يتم فيها تحديد ذلك.

- راجع قسم إعداد برنامج تشغيل VDMA للحصول على تفاصيل حول جانب SDK.

الساعات وإعادة التعيين

لقد وجدت أن أهم جوانب أي مشروع منطقي قابل للبرمجة هو النظر بعناية في مجالات الساعة وإعادة تعيين الإشارات. إذا تم تكوينها بشكل صحيح ، فلديك فرصة جيدة في جعل تصميمك يعمل.

ساعة البكسل والتوقيت مغلق

من أجل التحقق من أن بعض الإشارات نشطة ، من الجيد ربط هذه الإشارات بمصابيح LED (ساعات ، إعادة ضبط ، أقفال ، إلخ). إشارتان وجدتهما مفيدتين في تتبعهما على لوحة جهاز الإرسال هما ساعة البكسل والإشارة "المقفلة" في AXI4-Stream إلى كتلة مخرج الفيديو ، والتي تخبرك أن توقيت الفيديو قد تمت مزامنته مع جهاز التحكم في التوقيت ومصدر الفيديو البيانات. لقد أضفت بعض المنطق إلى غلاف كتلة التصميم الذي يتتبع ساعة البكسل باستخدام إشارة PixelClkLocked على كتلة dvi2rgb كإعادة تعيين. لقد أرفقت الملف باسم hdmi_wrapper.v هنا. ملف القيود مرفق هنا أيضًا.

الخطوة 2: قم بتكوين Zynq Programmable Logic for Receiver

كتلة المنطق القابلة للبرمجة لجهاز الاستقبال أبسط. يتمثل الاختلاف الرئيسي ، بخلاف كتل إدخال hdmi المفقودة ، في عدم وجود ساعة بكسل مستردة. لهذا السبب علينا إنشاء منطقتنا من معالج الساعة. يجب أن يتم هذا التصميم في مشروع منفصل عن جهاز الإرسال. لأغراضنا ، اتبع مشروع جهاز الاستقبال لوحة Zybo 7Z-20 بينما اتبع جهاز الإرسال لوحة Z7-10. تختلف FPGAs الموجودة على اللوحات ، لذا … كن حذرًا.

فيما يلي خطوات إنشاء قالب تصميم جهاز الاستقبال:

-

أضف كتل IP التالية إلى تصميمك:

- تحكم التوقيت

- AXI4- دفق إلى مخرج الفيديو

- RGB إلى DVI

- AXI VDMA

- AXI GPIO

- نظام المعالجة

- معالج الساعة

- ثابت (VDD مضبوط على 1)

- اتبع نفس النمط لتكوين هذه الكتل مثل جهاز الإرسال. تم تضمين صور للاختلافات الملحوظة في التكوين هنا. يظل الآخرون مثل المرسل.

- قم بتكوين VDMA لهذا التصميم كقناة قراءة فقط. قم بتعطيل قناة الكتابة.

-

يجب تكوين معالج الساعة للمخرجات التالية:

- clk_out1: 75 ميجا هرتز (ساعة بكسل)

- clk_out2: 150 ميجا هرتز (ساعة البث)

- clk_out3: 50 ميجا هرتز (ساعة أكسي لايت)

- قم بتوصيل كتل الفيديو كما هو موضح في صورة تصميم مجموعة RX.

- ثم قم بتشغيل أتمتة الاتصال ، والتي ستضيف كتل AXI Interconnect و AXI SmartConnect و System Reset وتحاول إجراء الاتصالات المناسبة. اذهب هنا ببطء للتأكد من أنه لا يقوم بإجراء اتصالات غير مرغوب فيها.

- اجعل ساعة HDMI TMDS ودبابيس البيانات خارجية على كتلة rgb2dvi

- لا حاجة لإشارة التوصيل الساخنة في هذا التصميم.

الخطوة 3: إعداد برنامج تشغيل VDMA

من الأفضل القيام بالإعداد للكتل المختلفة التي تم تكوينها عبر واجهة AXI-Lite باستخدام المشاريع التجريبية المضمنة في BSP كمرجع. بعد تصدير أجهزة التصميم وتشغيل SDK من Vivado ، سترغب في إضافة حزمة دعم جديدة للوحة وتضمين مكتبة lwip202 في نافذة إعدادات BSP. افتح ملف ملف system.mss من BSP وسترى برامج التشغيل الطرفية الموجودة من تصميم الكتلة الخاص بك. يتيح لك خيار "استيراد أمثلة" استيراد المشاريع التجريبية التي تستخدم هذه الأجهزة الطرفية وبالتالي يوضح لك كيفية تكوينها في البرنامج باستخدام برامج تشغيل Xilinx المتاحة (انظر الصورة المرفقة).

كانت هذه هي الطريقة المستخدمة لتكوين VDMA والمؤقت والمقاطعة و GPIO. تم تضمين الكود المصدري لكل من الإرسال والاستقبال هنا. الاختلافات تكاد تكون حصرية في main.c.

*** ملاحظة: نظرًا لأن النظام لا يعمل بكامل طاقته وقت كتابة هذا البرنامج التعليمي ، فإن الكود المصدري في هذا القسم لا يتضمن رمز الشبكة اللاسلكية. يجب معالجة العديد من الأخطاء كنتيجة للجمع بين مشاريع إرسال / استقبال الفيديو الأساسية مع مشاريع إرسال / استقبال الشبكة. لذلك يعالجهم هذا البرنامج التعليمي بشكل منفصل في الوقت الحالي. ***

وظيفة معالج مقاطعة TX (IRQHandler)

تقرأ هذه الوظيفة الرموز الرمادية التي يوفرها كل من VDMAs للقراءة والكتابة عبر كتل GPIO. يتم تحويل الرموز الرمادية إلى رقم عشري وتستخدم لتحديد موقع ذاكرة الإطار الأساسي للإطار الحالي. الإطار المنسوخ هو الإطار السابق للإطار الذي تمت كتابته بواسطة VDMA (على سبيل المثال ، إذا كان VDMA يكتب إلى الإطار 2 ، فإننا ننسخ الإطار 1 ؛ إذا كنا نكتب إلى الإطار 0 ، فإننا نلتف ونقرأ من الإطار 2).

تلتقط الوظيفة كل إطار سادس لتقليل معدل الإطارات إلى 10 هرتز بدلاً من 60 هرتز. الحد الأعلى للشبكة 300 ميجابت في الثانية. بمعدل 10 إطارات في الثانية ، يلزم عرض نطاق ترددي قدره 221.2 ميجابت في الثانية.

سيسمح التعليق / إلغاء التعليق على سطرين في هذه الوظيفة للمستخدم بالتغيير إلى وضع تمرير HDMI لأغراض التصحيح / الاختبار (يتم التعليق على الكود للإشارة إلى الأسطر المناسبة). يقوم حاليًا بنسخ الإطار إلى موقع ذاكرة يستخدمه رمز إيثرنت.

وظيفة معالج مقاطعة RX (IRQHandler)

تشبه هذه الوظيفة إلى حد كبير وظيفة TX ، ولكنها تنسخ من مخزن مؤقت 2 FIFO تستخدمه شبكة إيثرنت لكتابة البيانات الواردة إليه. يشير رمز الإيثرنت إلى الإطار الذي تتم الكتابة إليه من FIFO ، ويتم نسخ البيانات من الإطار المعاكس. يتم نسخ البيانات إلى الإطار مباشرة خلف الإطار الذي يقرأه VDMA لتجنب التمزق.

الخطوة 4: إعداد شبكة Nanorouter

من أجل إنشاء شبكة باستخدام TPlink nanorouters ، قم بتشغيلها بشكل فردي والاتصال بـ wifi SSID الافتراضي للأجهزة. يمكن العثور على مزيد من المعلومات حول إعدادات التكوين لهذا الجهاز المعين من خلال دليل مستخدم الجهاز.

قم بإعداد أحد الأجهزة كنقطة وصول ، وسيعمل هذا بمثابة الاتصال الأساسي للشبكة. تأكد من تسمية الشبكة وتدوين الاسم وتعطيل DHCP (لا نريد أن يقوم جهاز التوجيه بتكوين عناوين IP ديناميكيًا ، فنحن نريد من لوحات Zybo المتلقية والمتلقية تعيين عناوين IP الخاصة بهم بحيث تكون متسقة). بعد التكوين ، تأكد من إعادة تشغيل الجهاز وإنشاء هذه الشبكة.

قم بإعداد الجهاز الآخر كعميل ، وتأكد من اتصاله بشبكة SSID التي قمت بإعدادها باستخدام الموجه النانوي الأول. مرة أخرى ، تأكد من تعطيل DHCP للعميل.

بمجرد انتهاء العميل وإعادة تشغيله ، يجب أن يتصل بجهاز التوجيه النانوي لنقطة الوصول (إذا لم يحدث ذلك ، فمن المحتمل أن تكون هناك مشكلة في تكوين أحد الأجهزة). ستلاحظ أن ضوء LED على العميل سيكون ثابتًا بمجرد توصيله بنقطة الوصول.

من المحتمل أن يستمر وميض مؤشر LED النانوي لنقطة الوصول في هذه المرحلة ، هذا جيد! يعني الضوء الوامض أنه غير متصل بجهاز آخر من منفذ إيثرنت الخاص به ، وبمجرد توصيله بـ Zybo تم تكوينه ، سيظل مؤشر LED ثابتًا مما يشير إلى اتصال شبكة ناجح.

الآن بعد أن أصبح لدينا إعداد nanorouters لدينا ، لدينا شبكة لاسلكية تسمح لنا بالتواصل من خلالها. ملاحظة مهمة هي أن طريقة التكوين الخاصة بنا للخوادم النانوية (كنقطة وصول وعميل) تسمح لنا بالتواصل من لوحة Zybo للإرسال إلى لوحة Zybo المستقبلة كما لو كان الاثنان متصلين بسلك إيثرنت واحد. هذا يجعل إعداد شبكتنا أقل صعوبة ، حيث من المحتمل أن يتضمن البديل تكوين لوحات Zybo للاتصال بالخادم بشكل صريح مع الاتصال المقصود.

بمجرد إعداد كلا الجهازين ، يتم تكوين nanorouters وجاهزة للتنفيذ في شبكة WIDI الخاصة بك. لا يوجد إقران محدد بين nanorouters ولوحات Zybo ، لأن نقطة الوصول أو العميل سيعمل إما لجهاز الإرسال أو الاستقبال.

الخطوة 5: إعداد نظام معالجة Zynq لنقل البيانات عبر إيثرنت

من أجل نقل بيانات HDMI من إحدى لوحات Zybo إلى الأخرى ، يجب علينا دمج بروتوكول Ethernet مع برنامج تشغيل VDMA الخاص بنا. هدفنا هنا هو دفق إطارات الفيديو الفردية عبر Ethernet الطرفية في نظام المعالجة ، بمعدل محدد يتوافق مع عرض النطاق الترددي لشبكتنا. بالنسبة لمشروعنا ، استخدمنا بروتوكول TCP الذي تم توفيره بواسطة LwIP API. نظرًا لأن كلا من أعضاء المشروع يفتقران إلى الخبرة نسبيًا فيما يتعلق بمرافق الشبكات ، فقد تم إجراء هذا الاختيار دون الاعتراف الكامل بالآثار والقيود التي ينطوي عليها برنامج التعاون الفني. كانت المشكلة الرئيسية في هذا التطبيق هي النطاق الترددي المحدود وحقيقة أنه غير مصمم بالفعل لغرض تبخير كميات كبيرة من البيانات. ستتم مناقشة الحلول البديلة لاستبدال برنامج التعاون الفني وتحسينه في هذا المشروع لاحقًا.

وصف موجز لـ TCP مع LwIP: يتم إرسال البيانات عبر الشبكة في حزم بحجم tcp_mss (الحجم الأقصى لمقطع TCP) ، والذي يبلغ بشكل عام 1460 بايت. سيؤدي استدعاء tcp_write إلى أخذ بعض البيانات المشار إليها بواسطة مؤشر وتكوين pbufs (مخازن الحزمة) للاحتفاظ بالبيانات وتوفير هيكل لعمليات TCP. يتم تعيين الحد الأقصى من البيانات التي يمكن وضعها في قائمة الانتظار في وقت واحد على أنها tcp_snd_buf (مساحة المخزن المؤقت لمرسل TCP). نظرًا لأن هذه المعلمة هي رقم 16 بت ، فإننا مقيدون بحجم مخزن مؤقت للإرسال يبلغ 59695 بايت (هناك بعض الحشو المطلوب في مخزن الإرسال المؤقت). بمجرد وضع البيانات في قائمة الانتظار ، يتم استدعاء tcp_output لبدء إرسال البيانات. قبل إرسال الجزء التالي من البيانات ، من الضروري أن يتم إرسال جميع الحزم السابقة بنجاح. تتم هذه العملية باستخدام وظيفة recv_callback ، حيث إنها الوظيفة التي يتم استدعاؤها عند رؤية الإقرار من جهاز الاستقبال.

يعد استخدام أمثلة المشاريع في Vivado SDK مفيدًا جدًا لتعلم كيفية تشغيل LwIP TCP ، وهو نقطة انطلاق جيدة لبدء مشروع جديد.

يكون الإجراء الخاص بجهاز إرسال WiDi كما يلي:

- قم بتهيئة شبكة TCP باستخدام استدعاءات وظيفة برنامج تشغيل LWIP المعدني.

- حدد أي وظائف رد اتصال ضرورية لعمليات الشبكة.

- قم بالاتصال بمستقبل WiDi عن طريق الاتصال بعنوان IP الخاص به والمنفذ (التكوين الخاص بنا: Receiver IP هو 192.168.0.9 ، اتصل بالمنفذ 7).

- عند انتهاء صلاحية مؤقت برنامج تشغيل VDMA ، أدخل TX ISR.

- تحديد المخزن المؤقت للإطار الحالي للوصول إليه بناءً على رمز VDMA الرمادي

- ضع المقطع الأول من البيانات في قائمة انتظار في مخزن إرسال TCP المؤقت

- قم بإخراج البيانات وتحديث المتغيرات المحلية لتتبع مقدار البيانات التي تم إرسالها للإطار الحالي.

- عند الوصول إلى رد الاتصال المستلم (تم إجراء استدعاء للوظيفة بعد حصول المرسل على إقرار باسترداد البيانات) ، اصطف المقطع التالي من البيانات في قائمة الانتظار.

- كرر الخطوتين 7 و 8 حتى يتم إرسال الإطار بالكامل.

- ارجع إلى حالة الخمول لانتظار مقاطعة المؤقت التالية للإشارة إلى أن الإطار الجديد جاهز (رجوع إلى الخطوة 4).

تأكد من إعداد إعدادات LwIP لحزمة دعم اللوحة كما هو موضح في الصورة أعلاه. جميع القيم افتراضية باستثناء tcp_snd_buf ، tcp_pueue_ooseq ، mem_size ، memp_n_tcp_seg. لاحظ أيضًا أنه يمكن إجراء تصحيح مفصل للأخطاء عن طريق تغيير معلمات BSP لمجموعة debug_options.

الخطوة 6: إعداد نظام معالجة Zynq لاستقبال البيانات عبر إيثرنت

ستعمل لوحة تطوير Zybo التي ستعمل كمستقبل لاسلكي بشكل مشابه لجهاز الإرسال. ستكون إعدادات حزمة دعم اللوحة لـ LwIP مماثلة لتلك الموجودة في الخطوة السابقة.

سيأخذ الجهاز حزمًا تحتوي على مقاطع إطار الفيديو من جهاز التوجيه النانوي ، وسيقوم بنسخ بيانات إطار الفيديو إلى مساحة المخزن المؤقت للإطار الثلاثي لاستقبال VDMA. من أجل تجنب الكتابة فوق أي بيانات ، يتم استخدام مخزن مؤقت مزدوج للبيانات (سنشير إليه باسم المخزن المؤقت للشبكة) عند جمع البيانات من جهاز التوجيه النانوي ، بحيث يمكن أن تستمر حركة مرور الشبكة في التدفق أثناء نسخ إطار الفيديو الكامل السابق إلى المخزن المؤقت VDMA.

يتطلب الإجراء الخاص بجهاز استقبال WiDi مهمتين ، إحداهما هي تلقي بيانات إيثرنت ، والأخرى هي نسخ إطارات الفيديو من المخزن المؤقت للشبكة إلى المخزن المؤقت للإطارات الثلاثية لـ VDMA.

مهمة استقبال إيثرنت:

- قم بتهيئة شبكة TCP باستخدام استدعاءات وظيفة برنامج تشغيل LWIP المعدني (الإعداد باستخدام عنوان IP الذي سيتصل به جهاز الإرسال ، 192.168.0.9 في منطقتنا)

- حدد أي وظائف رد اتصال ضرورية لعمليات الشبكة.

- عند استلام حزمة إيثرنت ، انسخ بيانات الحزمة إلى المخزن المؤقت للشبكة الحالي ، وقم بزيادة البيانات المتراكمة الحالية.

- إذا كانت الحزمة تملأ المخزن المؤقت لإطار الشبكة ، فتابع إلى الخطوتين 5 و 6. وإلا ، فارجع إلى الخطوة 3 من هذه المهمة.

- إشارة إلى أن مهمة المخزن المؤقت للإطار الثلاثي VDMA يجب نسخها من المخزن المؤقت للشبكة المنتهي حديثًا.

- قم بالتبديل إلى المخزن المؤقت للشبكة الأخرى واستمر في جمع البيانات عبر إيثرنت.

- خامل حتى يتم استلام حزمة إيثرنت جديدة (الخطوة 3).

نسخ المخزن المؤقت للشبكة إلى المخزن المؤقت للإطارات الثلاثية VDMA:

- عند انتهاء صلاحية مؤقت برنامج تشغيل VDMA ، أدخل RX ISR.

- تحديد المخزن المؤقت للإطار الحالي للوصول إليه بناءً على رمز VDMA الرمادي.

- حدد المخزن المؤقت للشبكة الذي سيتم نسخه إلى المخزن المؤقت VDMA ، وانسخ تلك البيانات

الخطوة 7: قم بتوصيل Zybo Boards بمصدر HDMI و HDMI Sink

قم الآن بتوصيل كبلات HDMI لكل من جهاز الاستقبال وجهاز الإرسال ، وبرمجة FPGA وتشغيل نظام المعالجة. من المحتمل أن يكون معدل الإطارات بطيئًا للغاية ، بسبب الحمل الهائل في عملية LwIP وعرض النطاق الترددي المحدود. إذا كانت هناك أية مشكلات ، فاتصل عبر UART وحاول تحديد أي تحذيرات أو أخطاء.

الخطوة 8: أفكار بديلة للتحسين

كانت المشكلة الكبيرة لهذا المشروع هي كمية البيانات اللازمة لإرسالها عبر wifi. كان هذا متوقعًا ، ومع ذلك فقد قللنا من تقدير التأثير الذي كان سيحدثه وأدى إلى مزيد من الصور المتتالية على الشاشة بدلاً من بث الفيديو. هناك عدة طرق لتحسين هذا المشروع:

- ضغط الفيديو في الوقت الحقيقي. سيؤدي ضغط إطار تغذية الفيديو الوارد إلى إطار بإطار إلى تقليل كمية البيانات المطلوبة لإرسالها عبر الشبكة بشكل كبير. من الناحية المثالية ، يمكن أن يتم ذلك في الأجهزة (وهي ليست مهمة سهلة) ، أو يمكن أن يتم ذلك في البرنامج باستخدام نواة ARM الأخرى لتشغيل خوارزميات الضغط (سيحتاج هذا إلى مزيد من التحليل للتأكد من أن التوقيت يعمل). توجد بعض مكونات ضغط الفيديو في الوقت الفعلي مفتوحة المصدر التي وجدناها على الويب ، لكن الغالبية منها هي IP.

- تنفيذ دفق Ethernet في الأجهزة بدلاً من البرامج. كان هناك الكثير من الحمل بسبب نقص المساحة المتاحة لقائمة انتظار البيانات الصادرة في جهاز الإرسال ، بسبب القيود المفروضة على حجم المقطع. هناك عملية أكثر فاعلية تتمثل في استخدام AXI Ethernet IP مع المخزن المؤقت FIFO أو DMA لتغذية البيانات فيه. سيؤدي ذلك إلى تقليل الأمتعة الإضافية من LwIP TCP والسماح بتدفق المزيد من البيانات.

الخطوة 9: إمكانية الوصول

يجب أن يكون المنتج الناتج لمشروع WiDi هذا عبارة عن زوج مدمج ومتكامل تمامًا من الأجهزة التي يمكن للمستخدم توصيلها بأي مصدر HDMI ثم نقل تدفق الفيديو إلى شاشة مزودة بإمكانية HDMI لاسلكيًا. ستحتوي الأجهزة على Zynq-7000 SoC الموجود على اللوحة المرجعية Zybo وستدمج أجهزة الشبكة الموجودة في أجهزة التوجيه النانوية TP-Link. من الناحية المثالية ، سيكون المستخدم قادرًا على التحكم في وحدة الإرسال من موقع منفصل داخل نظام التشغيل المستهدف ، مع قليل من الحاجة إلى قدرة فنية كبيرة.

الأمان والاتصال

يجب أن تتضمن الأجهزة أيضًا بروتوكول أمان طبقة النقل (TLS) ولديها قدرة محدودة على الاتصال التلقائي ، وذلك لأغراض الخصوصية. يهدف المصممون إلى جعل الاتصال بشاشة عرض عبر واجهة لاسلكية إجراءً متعمدًا نيابة عن المستخدم لتجنب البث الخاطئ لمواد حساسة.

الوضع الحالي

حتى هذه النقطة ، لا تزال حالة المشروع قيد التنفيذ إلى حد كبير. لكي يستفيد المستخدم النهائي الحالي من هذا البرنامج التعليمي ، يجب أن يكون لديه فهم تقني قوي لتصميم النظام المضمن ويجب أن يكون لديه بعض الإلمام بالأجهزة القابلة للبرمجة والبرامج المضمنة التي تعمل معًا.

البيانات التي يتم إرسالها عبر الشبكة غير مشفرة في هذه المرحلة ويفترض أنها نقل أولي لحزم TCP / IP.

تم اختبار مشروع الفيديو الأساسي بنجاح لكل من الإرسال والاستقبال. من ناحية أخرى ، تم إنشاء الاتصال اللاسلكي بين لوحين zybo وتم إرسال بيانات إطار الاختبار بنجاح. ومع ذلك ، لا يزال من الضروري دمج رمز الشبكة لكل مشروع أساسي للفيديو واختبار إرسال إطارات الفيديو الفعلية.

موصى به:

تطوير مجلس Drivemall: 5 خطوات

تطوير لوحة Drivemall: في هذا البرنامج التعليمي سنرى الخطوات الأساسية لإنشاء لوحة Arduino مخصصة. البرنامج المستخدم هو KiCad لتصميم اللوحة و Arduino IDE لإنشاء وتحميل البرامج الثابتة للوحة

درع مجلس تطوير Mojo FPGA: 3 خطوات

درع مجلس تطوير Mojo FPGA: قم بتوصيل لوحة تطوير Mojo الخاصة بك بالمدخلات الخارجية باستخدام هذا الدرع. اللوحة مصنوعة من قبل Alchitry. FPGA مفيدة جدًا

مجلس تطوير JALPIC One: 5 خطوات (بالصور)

مجلس تطوير JALPIC One: إذا اتبعت مشاريع Instructables الخاصة بي ، فأنت تعلم أنني معجب جدًا بلغة برمجة JAL جنبًا إلى جنب مع PIC Microcontroller. JAL هي لغة برمجة تشبه باسكال تم تطويرها للميكروكونترولر 8 بت PIC من Microchip. مو

تصميم مجلس تطوير وحدة التحكم الدقيقة: 14 خطوة (بالصور)

تصميم مجلس تطوير وحدة التحكم الدقيقة: هل أنت صانع ، أو هاوٍ ، أو متسلل مهتم بالتقدم من مشاريع اللوح المثالي ، و DIP ICs ، وثنائي الفينيل متعدد الكلور محلي الصنع إلى ثنائي الفينيل متعدد الكلور متعدد الطبقات مصنوع من قبل بيوت متنقلة و تغليف SMD جاهز للإنتاج بالجملة؟ ثم هذه التعليمات لك! هذا GUI

السيد E.Z. مجلس تطوير الأنبوب: 4 خطوات (بالصور)

السيد E.Z. مجلس تطوير الأنبوب: الهدف / الغرض: السيد إ. Tube عبارة عن منصة صوتية ذات أنبوب مفرغ رخيص بدون "الحديد": لا يوجد محول طاقة ، لا يوجد محول (محولات) إخراج. عادةً ما يحتوي مضخم الصوت الأنبوبي على العديد من المحولات الثقيلة والمكلفة: محولات الإخراج التي تحمي الكلام