جدول المحتويات:

- مؤلف John Day day@howwhatproduce.com.

- Public 2024-01-30 07:41.

- آخر تعديل 2025-01-23 12:54.

هذا برنامج تعليمي حول كيفية إنشاء ساعة توقيت دقيقة واحدة باستخدام VHDL ولوحة Basys 3. هذا الجهاز مثالي للألعاب حيث يكون لكل لاعب دقيقة واحدة كحد أقصى للقيام بنقله. تعرض ساعة الإيقاف بدقة الثواني والميلي ثانية على الشاشة ذات الأجزاء السبعة ، بدءًا من 0 ثانية و 0 مللي ثانية ، حتى 60 ثانية و 0 مللي ثانية. كما يتم استخدام زرين: الزر المركزي المستخدم لبدء تشغيل المؤقت وإيقافه ومتابعته ، والزر الأيمن يستخدم لإعادة تشغيل المؤقت. عند مقارنة الجهاز جنبًا إلى جنب مع ساعة الإيقاف المدمجة بهاتف ذكي ، تكون دقة الساعة ملحوظة.

الخطوة 1: الحصول على الأجهزة / البرامج

1. لوحة تدريب Basys 3 Artix-7 FPGA من Digilent مع كابل Micro-USB إلى USB

2. Vivado 2016.2 Design Suite من Xilinx

الخطوة 2: مخطط الكتلة

يتم إنشاء هذه الدائرة بشكل سلوكي وتستخدم مكونات Xilinx المضمنة ، ولكن يمكن أيضًا وصفها هيكليًا ، كما هو موضح في الرسم التخطيطي الهيكلي العام أعلاه. من الرسم البياني ، يمكن ملاحظة أن الدائرة مدفوعة بفاصلين تردد. يعمل أحد فواصل التردد عند 1 سنتي ثانية ويقود عداد الكاثود الذي يتم استخدامه كأرقام معروضة على الشاشة المكونة من سبعة أجزاء. يعمل مقسم التردد الثاني عند 240 هرتز ويستخدم لقيادة عداد الأنود الذي يدور عبر الأنودات بحيث يتم عرض جميع الأرقام بشكل صحيح على الشاشة المكونة من سبعة أجزاء. يأخذ المشفر منطق الكاثود من عداد الكاثود ومنطق الأنود من عداد الأنود ، ويقوم بترميزه إلى كاثود الإخراج والأنود الذي يقوم بتشغيل العرض المكون من سبعة أجزاء. وظيفة هذا المشفر هي أن يتغير خرج الكاثود في كل مرة يتغير فيها إخراج الأنود. لا يمكن تشغيل خرج الكاثود بشكل مستقل عن العداد لأن الأنودات يجب أن تدور خلال 4 أرقام منفصلة.

الخطوة 3: وحدة المشروع

أولاً ، يتم إجراء كتلة عملية لـ CEN بحيث يتم تبديل ENABLE عند اكتشاف زر الضغط. هذا بمثابة إيقاف / بدء عداد الكاثود.

في كتلة العملية التالية ، يتم تعيين إشارات الساعة المئوية الثانية و 240 هرتز بحيث تزيد العدادات الخاصة بها بمقدار 1 في كل مرة تصل فيها الساعة الداخلية 100 ميجا هرتز إلى حافة صاعدة. بمجرد أن يصل عداد السنتيس ثانية إلى 500000 ، سوف يعيد ضبطه مرة أخرى إلى 0. وفي الوقت نفسه ، سيتم إعادة تعيين عداد 240 هرتز بمجرد وصول العد إلى 41667.

بالنسبة لقسم الكاثود في الكود ، إذا كان ENABLE هو "0" ، فسيتوقف حساب الكاثود مؤقتًا. إذا تم الضغط على زر إعادة الضبط خلال هذا الوقت ، فسيتم إعادة تعيين جميع الأعداد إلى "0000". وفي الوقت نفسه ، إذا كان ENABLE هو "1" ، فسيستمر عد الكاثود حتى يصل عدد الكاثود إلى 60.00 ، حيث يقوم بتشغيل إشارة التوقف لتكون "1". توجه إشارة الإيقاف إلى كتلة عملية CEN وتتسبب في أن يكون ENABLE "0" بينما تكون إشارة الإيقاف "1" ولن تتغير حتى يتم الضغط على زر إعادة الضبط.

أخيرًا ، يتم إعداد عرض المقاطع السبعة من خلال توصيل الأنودات الأربعة بشكل صحيح مع كل من الكاثودات الثمانية لعرض الأرقام الخاصة بها من 0 إلى 9 في وقت واحد.

الخطوة 4: القيود

يربط ملف القيود هذا المدخلات والمخرجات المحددة من VHDL إلى الأجزاء المادية الضرورية من لوحة Basys. بالنسبة لهذا المشروع ، تشتمل المكونات على أربعة أنودات وكل من كاثوداتها الثمانية لشاشة العرض السبعة ، والساعة الداخلية 100 ميجا هرتز ، والزر الأوسط ، والزر الأيمن.

الخطوة 5: الاختبار

بمجرد الانتهاء من الرمز ، يمكنك الآن برمجة FPGA عبر كابل USB. يجب أن يظهر عرض المقاطع السبعة 0.00. اختبر لمعرفة ما إذا كانت الأزرار تعمل بالضغط على الزر المركزي لبدء المؤقت حتى يصل إلى 60.00 ويتوقف ؛ في أي وقت بينهما ، يمكنك الضغط على الزر المركزي مرة أخرى لإيقافه مؤقتًا. بمجرد إيقافه مؤقتًا ، يمكنك الضغط على الزر الأيمن لإعادة تعيين المؤقت إلى 0.00. إذا كان كل شيء يعمل بشكل صحيح ، فتهانينا لقد بنيت للتو مؤقتًا لمدة دقيقة واحدة!

موصى به:

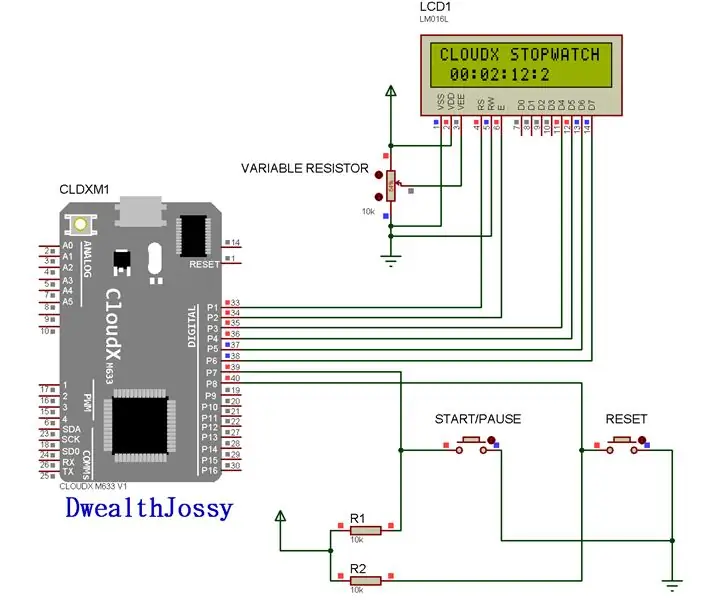

ساعة توقيت رقمية بسيطة كلاودكس M633: 4 خطوات

Simple CloudX M633 Digital Stopwatch: في هذا المشروع ، سنصنع نسخة من ساعة رقمية يمكنها الاحتفاظ بسجل للساعات والدقائق والثواني ، تمامًا مثل ساعة التوقيت على هاتفك المحمول! سنستخدم شاشة LCD لعرض الوقت

ساعة توقيت أساسية باستخدام لوحة VHDL و Basys3: 9 خطوات

ساعة توقيت أساسية باستخدام لوحة VHDL و Basys3: مرحبًا بك في التعليمات حول كيفية إنشاء ساعة توقيت باستخدام لوحة VHDL و Basys 3 الأساسية. نحن متحمسون لمشاركة مشروعنا معك! كان هذا المشروع النهائي لدورة CPE 133 (التصميم الرقمي) في Cal Poly ، SLO في خريف 2016. المشروع الذي نبنيه

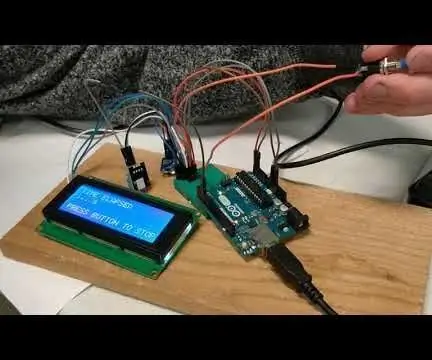

ساعة اردوينو بسيطة / ساعة توقيت: 6 خطوات (مع صور)

ساعة اردوينو بسيطة / ساعة توقيت: هذه & quot؛ قابلة للتوجيه & quot؛ سيُظهر لك ويعلمك كيفية إنشاء ساعة Arduino Uno بسيطة تعمل أيضًا كساعة توقيت في بضع خطوات بسيطة فقط

ساعة توقيت VHDL: 8 خطوات (بالصور)

VHDL Stopwatch: هذا برنامج تعليمي حول كيفية صنع ساعة توقيت باستخدام VHDL ولوحة دائرة FPGA ، مثل لوحة Basys3 Atrix-7. ساعة الإيقاف قادرة على العد من 00.00 ثانية إلى 99.99 ثانية. يستخدم زرين ، أحدهما لزر البدء / الإيقاف والآخر من أجل

طريقة الإسفنج + كلوريد الحديديك - حفر ثنائي الفينيل متعدد الكلور في دقيقة واحدة!: 5 خطوات (بالصور)

طريقة الإسفنج + كلوريد الحديديك - حفر ثنائي الفينيل متعدد الكلور في دقيقة واحدة!: في هذا Instructable ، سأوضح لك كيفية حفر لوحة دائرة بحوالي ملعقة كبيرة من محلول نقش كلوريد الحديديك وإسفنجة مربعة بحجم 2 بوصة. ستندهش عندما يختفي النحاس المكشوف الموجود على ثنائي الفينيل متعدد الكلور أمام عينيك ، ويختفي خنزيرك