جدول المحتويات:

- مؤلف John Day day@howwhatproduce.com.

- Public 2024-01-30 07:41.

- آخر تعديل 2025-01-23 12:54.

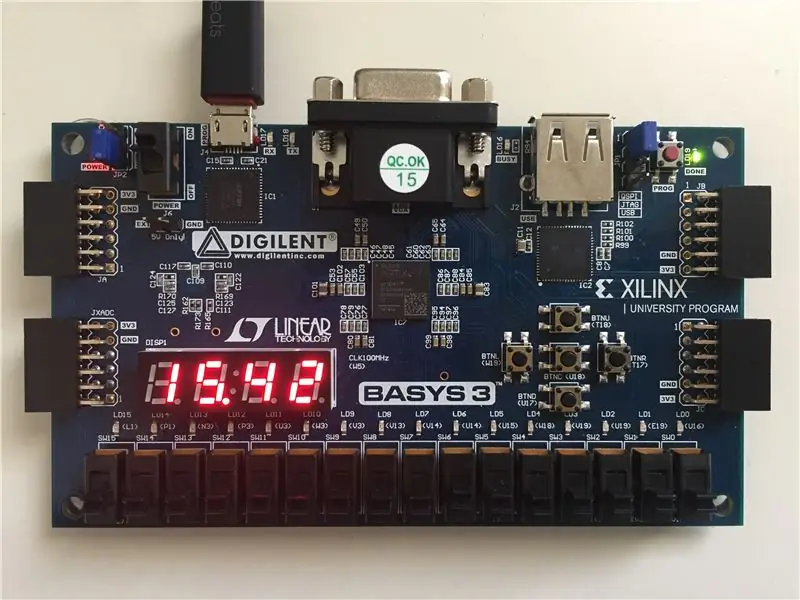

هذا برنامج تعليمي حول كيفية صنع ساعة توقيت باستخدام VHDL ولوحة دائرة FPGA ، مثل لوحة Basys3 Atrix-7. ساعة الإيقاف قادرة على العد من 00.00 ثانية إلى 99.99 ثانية. يستخدم زرين ، أحدهما لزر البدء / الإيقاف والآخر لزر إعادة الضبط. يتم عرض الأرقام على شاشة اللوحة ذات الأجزاء السبعة باستخدام الأنودات والكاثودات. هناك ثلاثة ملفات مختلفة مطلوبة لتشغيل ساعة الإيقاف هذه.

الخطوة 1: الأجهزة / البرامج

- لوح Basys3 Atrix-7 FPGA

- جناح تصميم Vivado من Xilinx

- USB 2.0 ذكر إلى Micro-B ذكر

الخطوة 2: مخطط الكتلة

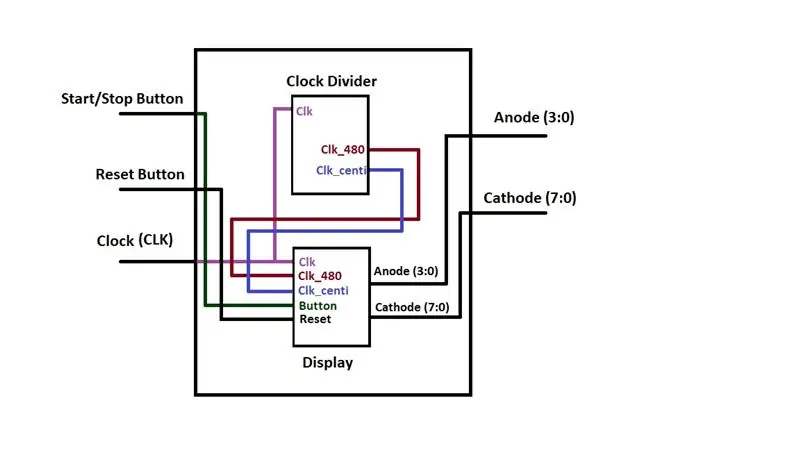

تحتوي ساعة الإيقاف الإجمالية على ثلاثة مدخلات ومخرجات. المدخلات الثلاثة هي البدء / الإيقاف ، وإعادة التعيين ، والساعة. زر البدء / الإيقاف وإعادة الضبط هما أزرار والساعة هي ساعة اللوحة 100 ميجاهرتز. المخرجات هما الأنودات والكاثودات للشاشة ذات الأجزاء السبعة.

الوحدة الأولى (مقسم الساعة) لها مدخل ومخرجان ، المدخل هو ساعة اللوحة 100 ميجاهرتز والمخرجات عبارة عن ساعتين منفصلتين ، واحدة تعمل بتردد 480 هرتز والأخرى تعمل بسرعة 0.5 ميجاهرتز.

تحتوي الوحدة الثانية (العرض) على خمسة مدخلات ومخرجين. المدخلات هي ساعة اللوحة 100 ميجاهرتز ، والساعتان من وحدة مقسم الساعة ، وأزرار البدء / الإيقاف وإعادة الضبط. النواتج هي الأنودات والكاثودات.

تحتوي الوحدة الأخيرة (على غرار مخطط الكتلة بالكامل) على ثلاثة مدخلات ومخرجين. هذا هو الملف الذي يجمع كل شيء معًا. المدخلات هي 100 ميجاهرتز للوحة وأزرار البدء / الإيقاف وإعادة الضبط. النواتج هي الأنودات والكاثودات التي تتحكم في عرض الأجزاء السبعة. جميع المدخلات والمخرجات موجودة فعليًا على السبورة للوحدة النهائية.

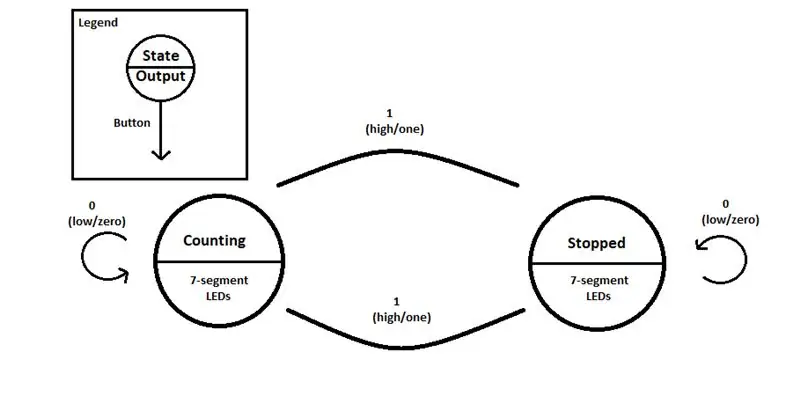

الخطوة 3: مخطط الحالة

توضح الصورة أعلاه مخطط الحالة لكيفية عمل ساعة الإيقاف. لا يؤثر الضغط على زر إعادة الضبط على حالة ساعة الإيقاف. يتم تحديد الحالة التالية بواسطة زر البدء / الإيقاف. تكون نقطة البداية / الإيقاف "عالية" عند الضغط عليها لأسفل ، ولكن ليس عند الضغط باستمرار ، و "منخفضة" عندما يرتد الزر للخلف أو يتم الضغط عليه بعد أن يكون "مرتفعًا" للحظات.

إذا كانت ساعة الإيقاف تحتسب وانتقل زر البدء / الإيقاف إلى "مرتفع" ، فإنه يتوقف عن العد. إذا تم إيقاف ساعة الإيقاف وانتقل زر البدء / الإيقاف إلى "مرتفع" ، فسيبدأ العد مرة أخرى. في كلتا الحالتين ، إذا كان زر البدء / الإيقاف "LOW" ، فسيظل في الحالة التي هو عليها حاليًا.

الخطوة 4: وحدة تقسيم الساعة

تحتوي وحدة مقسم الساعة على مدخل واحد ، وساعة اللوحة 100 ميجاهرتز ، ومخرجان ، وهما الساعتان 480 هرتز و 0.5 ميجاهرتز. يتم استخدام الساعة 480 هرتز للاحتفاظ بجميع مصابيح LED على شاشة العرض المكونة من سبعة أجزاء "قيد التشغيل" في نفس الوقت عن طريق التبديل بين الأربعة بسرعة. يتم استخدام الساعة 0.5 ميجا هرتز لساعة الإيقاف في العد فعليًا بمقدار سنتي ثانية.

الخطوة 5: وحدة العرض

تحتوي وحدة العرض هذه على خمسة مدخلات ، وساعة اللوحة 100 ميجاهرتز ، وساعتان من وحدة الساعة ، وأزرار البدء / الإيقاف وإعادة الضبط ، ومخرجان ، الأنودات والكاثودات. تحتوي هذه الوحدة أيضًا على "المنطق" لكيفية حساب ساعة الإيقاف وتضمين آلة الحالة المحدودة.

الخطوة 6: وحدة الربط

هذه الوحدة النهائية هي التي تجمع الوحدتين الأخريين معًا. يحتوي على ثلاثة مدخلات ، ساعة اللوحة 100 ميجاهرتز وأزرار البدء / الإيقاف وإعادة الضبط ، ومخرجان ، الأنودات والكاثودات. تنتقل الساعة 100 ميجاهرتز إلى وحدة مقسم الساعة ووحدة العرض ، وتنتقل أزرار البدء / الإيقاف وإعادة الضبط إلى وحدة العرض. تنتقل مخرجات وحدة مقسم الساعة (480 هرتز و 0.5 ميجاهرتز) إلى مدخلي الساعة لوحدة العرض. تنتقل مخرجات وحدة العرض (الأنودات والكاثودات) إلى مخرجات الوحدة النهائية.

الخطوة 7: القيود

يمكن أن يكون المدخلان أي أزرار على لوحة Basys3 Atrix-7 FPGA وستكون المخرجات هي الأنودات الأربعة والكاثودات الثمانية (لأنك تريد أيضًا نقطة عشرية بين الثواني والميلي ثانية) لشاشة الأجزاء السبعة.

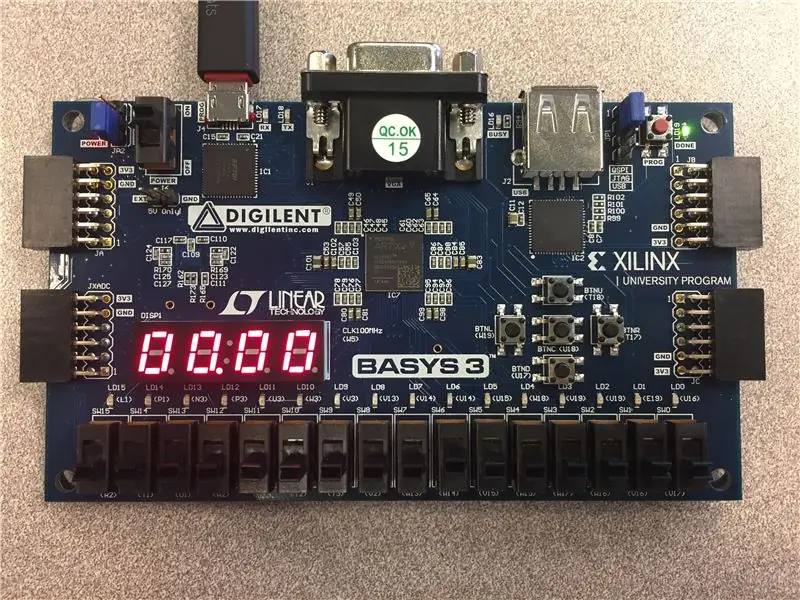

الخطوة 8: تم

قم بتحميل البرنامج على لوحة Basys3 Atrix-7 FPGA واضغط على زر البدء / الإيقاف لبدء تشغيل ساعة الإيقاف!

موصى به:

كيفية عمل ساعة توقيت باستخدام Arduino: 8 خطوات (بالصور)

كيفية إنشاء ساعة توقيت باستخدام Arduino: هذه ساعة إيقاف بسيطة للغاية من Arduino 16 * 2 Lcd ……….. إذا كنت تحب هذا التعليمات ، يرجى الاشتراك في قناتي https://www.youtube.com / ZenoModiff

ساعة توقيت أساسية باستخدام لوحة VHDL و Basys3: 9 خطوات

ساعة توقيت أساسية باستخدام لوحة VHDL و Basys3: مرحبًا بك في التعليمات حول كيفية إنشاء ساعة توقيت باستخدام لوحة VHDL و Basys 3 الأساسية. نحن متحمسون لمشاركة مشروعنا معك! كان هذا المشروع النهائي لدورة CPE 133 (التصميم الرقمي) في Cal Poly ، SLO في خريف 2016. المشروع الذي نبنيه

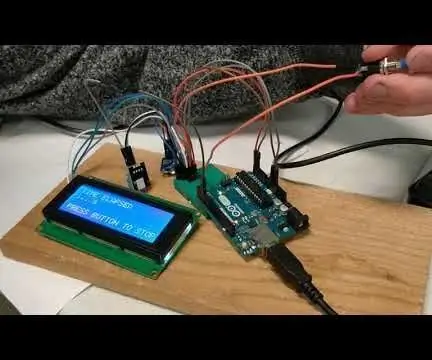

ساعة توقيت اردوينو: 4 خطوات (بالصور)

Arduino Stopwatch: سيوضح لك هذا Instructable كيفية إنشاء ساعة إيقاف من Arduino

ساعة اردوينو بسيطة / ساعة توقيت: 6 خطوات (مع صور)

ساعة اردوينو بسيطة / ساعة توقيت: هذه & quot؛ قابلة للتوجيه & quot؛ سيُظهر لك ويعلمك كيفية إنشاء ساعة Arduino Uno بسيطة تعمل أيضًا كساعة توقيت في بضع خطوات بسيطة فقط

ساعة توقيت VHDL دقيقة واحدة: 5 خطوات

ساعة توقيت دقيقة واحدة VHDL: هذا برنامج تعليمي حول كيفية إنشاء ساعة توقيت دقيقة واحدة باستخدام VHDL ولوحة Basys 3. هذا الجهاز مثالي للألعاب حيث يكون لكل لاعب دقيقة واحدة كحد أقصى للقيام بنقله. تعرض ساعة الإيقاف بدقة الثواني والميلي ثانية