جدول المحتويات:

- مؤلف John Day day@howwhatproduce.com.

- Public 2024-01-30 07:36.

- آخر تعديل 2025-01-23 12:53.

JDM هو مبرمج PIC شائع لأنه يستخدم منفذًا تسلسليًا ، وهو الحد الأدنى من المكونات ولا يتطلب أي مصدر طاقة. ولكن هناك ارتباك هناك ، مع وجود العديد من اختلافات المبرمجين على الشبكة ، أي منها يعمل مع أي بلدان جزر المحيط الهادئ؟ في هذا "التوجيه" ، نضع JDM في الاختبار وأشرح كيفية محاكاة الدائرة باستخدام Spice والتي ستجيب على جميع أسئلتك!

اللوازم

LTspice الذي يمكن تنزيله من الأجهزة التناظرية هنا.

تحتاج أيضًا إلى ملفات دائرة JDM هنا.

الخطوة 1: متطلبات المنفذ التسلسلي

تتطلب JDM منفذًا تسلسليًا يفي بمواصفات EIA232 ، من الناحية المثالية مع + 12 / -12 مستويات الجهد.

وفقًا لورقة بيانات Texas Instruments Line Driver MC1488 (الشكل 3)

مقاومة الإخراج = 4V / 8mA = 500 أوم.

حد تيار الدائرة القصيرة = 12mV ، مع عدم وجود حد زمني - لا ضرر للرقاقة.

يوصى بمقاومة إدخال جهاز استقبال الخط = 3 كيلو إلى 7 كيلو أوم.

تستخدم المنافذ التسلسلية على أجهزة الكمبيوتر المكتبية القديمة + 12 فولت / -12 فولت لتلبية هذا المطلب.

تستخدم المنافذ التسلسلية في أجهزة الكمبيوتر المحمولة الأحدث جهدًا أقل. قد يعمل التهاب الجلد والعضلات لدى الأطفال وقد لا يعمل - الإجابة أكثر تعقيدًا.

الخطوة الثانية: متطلبات برمجة الموافقة المسبقة عن علم

يتم الحصول على المعلومات المتعلقة بمتطلبات برمجة الموافقة المسبقة عن علم من Microchip. ما ورد أعلاه لجهاز نموذجي.

الخطوة 3: مواصفات JDM

هل فُقد موقع ويب JDM الأصلي في ضباب الزمن؟ هذا يتركنا نخمن ما قصده المصمم في الأصل للمواصفات.

- قم بتوفير VDD = 5V ، وما يصل إلى IDD = 2mA كحد أقصى (لإصدار "in socket")

- قم بتوفير VHH = 13V ، وحتى IHH = 0.2mA كحد أقصى.

- MCLR وقت الارتفاع tVHHR = 1uS كحد أقصى.

- يجب أن يكون إصدار ICSP قادرًا على سحب MCLR منخفضًا مقابل سحب 22k للهدف.

الخطوة 4: وصف الدائرة

يعتمد الشكل JDM1 على دائرة JDM "القياسية" المأخوذة من موقع الويب PICPgm. هذا هو مبرمج "PIC in Socket" حيث تأخذ PIC الطاقة من دبابيس TX و RTS. كان من الصعب فهم الرسم التخطيطي الأصلي ، لذا أعدت رسمه باستخدام الاصطلاح العادي لتدفق التيار من أعلى إلى أسفل. وقد أضفت مؤشرات LED "RESET" و "PROG" و "RTS" والتي تعتبر ضرورية أثناء البناء والاختبار. نأمل ألا يكون لها أي تأثير ضار على السلوك.

يتمثل العرف الطبيعي لتصميم الدوائر في جميع الأسباب ، ولكن الميزة الرئيسية لـ JDM هي أن أرض المنفذ التسلسلي (GND) متصلة بـ VDD. يؤدي هذا إلى حدوث ارتباك حيث يتم قياس إشارات المنفذ التسلسلي فيما يتعلق بإشارات GND و PIC فيما يتعلق بالأرض المنطقية (VSS).

عندما يرتفع TX ، يتصرف Q1 كثنائيين متحيزين للأمام. (جامع Q1 ليس متحيزًا عكسيًا كما هو الحال مع عملية الترانزستور العادية). Q1 يشحن جامع C2 ، وهو مثبت في VDD + 8V بواسطة Zener (D3). يسلم باعث Q1 13 فولت إلى MCLR لوضع البرنامج / التحقق.

عندما ينخفض TX ، يتم شحن المكثف C3 من خلال D1 ويتم تثبيت VSS عند VDD-5V بواسطة zener (D5). كما يتم تثبيت TX عند (VSS-0.6) بواسطة D1. Q1 متوقف ، C1 يحتفظ بشحنه لنبض البرمجة التالي. يتم تثبيت MCLR عند 0V بواسطة D2 ، لذلك تم إعادة تعيين PIC الآن.

عندما تكون RTS عالية ، يتم إرسال الساعة إلى PGC. D4 clamp PGC عند منطق VDD عالي. عندما يكون RTS منخفضًا ، يتم شحن المكثف C3 من خلال D6 ويتم تثبيت VSS عند VDD-5V بواسطة zener (D5). D6 المشابك PGC في VSS أو المنطق 0.

أثناء البرمجة ، تتم قراءة البيانات المرسلة على DTR على PGD ، والتي تقوم PIC بتكوينها كمدخلات. عندما يكون DTR مرتفعًا ، يعمل Q2 كـ "تابع باعث" ويكون جهد PGD حوالي (VDD-0.6) أو منطق 1. عندما يكون DTR منخفضًا ، يعمل Q2 كترانزستور سيئ (دبابيس الباعث والمجمع معكوسة). يسحب Q2 انخفاض PGD ، والذي يتم تثبيته بواسطة D7 عند VSS أو المنطق 0.

أثناء التحقق ، يقوم PIC بتكوين PGD كمخرج لإرسال البيانات إلى المنفذ التسلسلي. يجب ضبط DTR على قيمة عالية ، وقراءة البيانات على CTS. عندما يكون خرج PGD مرتفعًا ، يكون Q2 متوقفًا ، CTS = DTR = + 12V. عندما يكون خرج PGD منخفضًا ، يكون Q2 قيد التشغيل. يقوم جامع Q2 بسحب التيار (12V + 5V) / (1k + 1k5) = 7mA من DTR ، ويسحب CTS منخفضًا ، إلى VSS.

الخطوة 5: الاستعداد للمحاكاة

قم بتنزيل LT spice ، واحفظ وافتح ملفات الدائرة (*.asc) المتوفرة هنا. لمحاكاة الدائرة ، يجب أن نعطيها بعض المدخلات ، ثم "تتبع" المخرجات. V1 ، V2 V3 يحاكي المنفذ التسلسلي 12 فولت بمقاومة الخرج R11 ، R12 ، R13.

- يولد V1 نبضتي برنامج عند الإرسال من 0.5 مللي ثانية إلى 4.5 مللي ثانية

- يولد V2 اندفاعا من نبضات البيانات على DTR من 1.5 إلى 4.5 مللي ثانية

- يولد V3 اندفاعا من نبضات الساعة على RTS من 0.5 إلى 3.5 مللي ثانية

المكونات V4 و X1 و R15 و R16 كلها جزء من المحاكاة.

- يولد V4 نبضتين من 2.5 إلى 4.5 مللي ثانية للتحقق من البيانات.

- تحاكي Jumper X1 الإخراج على PGD.

- R15، R16 تحاكي "تحميل" الموافقة المسبقة عن علم على VDD و MCLR.

الخطوة 6: التعديلات على ICSP

يوضح الشكل JDM3 إصدار البرمجة "داخل الدائرة". التعديلات من الأصل

- استبدل مقبس ZIF بموصل ICSP.

- يتم تشغيل PIC الآن عن طريق الإمداد بالدائرة المستهدفة (V5).

- قم بإزالة 5V zener (D5).

- يتم تحريك المكثف الصغير 100pF (C4) بجوار PIC على الدائرة المستهدفة.

- تأخذ مصابيح LED الطاقة من لوحة الدوائر حيثما أمكن ذلك.

- مطلوب مقاومة سحب MCLR (R10) والصمام الثنائي (D10) في الدائرة المستهدفة.

- تحذير. يجب أن تحتوي اللوحة المستهدفة على مصدر إمداد "عائم" ، وبطارية مثالية.

- لا تقم بتوصيل الأرض المستهدفة (VSS) بأرض الكمبيوتر / الكمبيوتر الشخصي عن طريق توصيل أي منافذ كمبيوتر أخرى في نفس الوقت مثل JDM.

بعد محاكاة JDM1 ، أصبحت مشكلة وقت الشحن الطويل على C2 واضحة. ثم بعد قراءة Fruttenboel ، يبدو أنه تمت إضافة C2 و Q1 كتعديل على الأصل. لا أستطيع التفكير في الغرض من C2 و Q1 بصرف النظر عن خلق المشاكل. لذلك بالنسبة لـ JDM4 ، نعود إلى التصميم الأقدم على Fruttenboel وهو تصميم بسيط ومباشر للفهم. المشبك D1 و D3 / LED2 MCLR بين VSS و VDD + 8V. يتم تقليل قيمة R1 إلى 3k3 ، وهو ما يكفي فقط لإضاءة LED2 عند 12V.

تم تصميم JDM4 أيضًا للعمل مع المنافذ التسلسلية الأضعف. عندما يرتفع TX (+ 9V) ، مصدر TX الحالي = (9-8) / (1k + 3k3) = 0.2ma ، يكفي فقط لسحب MCLR عاليًا على الرغم من أنه غير كافٍ لإضاءة LED2. عندما ينخفض TX (حوالي -7V) ، فإن حوض تيار TX = (9-7) / 1k = 2mA. تيار LED1 = (7-2 لمصباح LED) / (2k7) = 1.8mA. تيار سحب MCLR = 7-5.5 / 3k3 = 0.5mA.

تم أيضًا اختبار هذه الدائرة (محاكاة JDM5) لمعرفة ما يحدث مع المنافذ التسلسلية +/- 7 فولت كحد أدنى ، حيث لا يوجد جهد كافي للحفاظ على VHH = 13 فولت. أصبح الغرض من C1 الآن واضحًا ، C1 تخلق دفعة قصيرة + ve إلى MCLR ، ارتفاع 33us على الحافة الصاعدة من TX ، طويلة بما يكفي لدخول PIC في وضع البرمجة ، ربما؟ لكن قم بإزالة العبور X2 (تعطيل LED1) حيث لا يوجد تيار كافٍ لسحب MCLR المنخفض وإضاءة LED1 معًا. عندما ينخفض TX ، فإن حوض تيار TX = (7V-5.5V) / (1k + 3k3) = 0.3mA ، يكفي فقط لسحب MCLR المنخفض مقابل السحب R10.

الخطوة 7: نتائج المحاكاة

لعرض ملفات الرسوم ، من الأفضل النقر بزر الماوس الأيمن فوق الروابط أدناه ، ثم تحديد "فتح الرابط في علامة تبويب جديدة"

المحاكاة 1: تتبع MCLR و VSS و RTS للأصل JDM1. تظهر الملاحظة 1 و 2 و 3 على الفور.

المحاكاة 2: تتبع MCLR و VSS و RTS لـ JDM2 المعدل ، والذي يعمل على إصلاح المشكلات السابقة.

المحاكاة 3: تتبع PGD و VSS و PGC لإرسال بيانات JDM2 في وضع البرنامج. الملاحظة 4 عند 3.5mS.

المحاكاة 4: تتبع PGD و VSS و CTS لـ JDM2 في وضع التحقق (تم إدخال وصلة مرور X1). نعم

المحاكاة 5: تتبع MCLR و VSS و PGD و PGC لـ JDM3. استخدام ICSP للطاقة من الدائرة يحل العديد من المشاكل.

المحاكاة 6: تتبع MCLR و VSS و PGD و PGC لـ JDM4 مع منفذ تسلسلي +/- 9 فولت. يرتفع MCLR على الفور ، ويعمل بشكل كامل.

المحاكاة 7: تتبع MCLR و VSS و TX لـ JDM5 مع إزالة +/- 7V المنفذ التسلسلي والعبور X2. ينشئ C1 دفعة + ve (ارتفاع) على الحافة الصاعدة لـ MCLR ، وهو ما يكفي تقريبًا لدفع MCLR فوق TX إلى 13V.

الخطوة 8: الاستنتاجات

Spice جيدة حقًا في الكشف عن "الأسرار الخفية" لتشغيل الدائرة. من الواضح أن دائرة JDM تعمل وتتوافق مع العديد من رقائق الموافقة المسبقة عن علم ، لكن الملاحظات التالية تكشف عن قيود / مشاكل / أخطاء توافق محتملة؟

- وقت ارتفاع طويل لـ MCLR بينما يتم شحن C2 إلى VPP على أول نبضة من TX. مواصفات الفشل 3.

- يقوم المنفذ التسلسلي بشحن C2 عندما ترتفع TX وتنخفض RTS. لكن RTS لديها أيضًا وظيفة شحن C3. عندما يحدث كلاهما في نفس الوقت ، يؤدي ذلك إلى مزيد من الحمل على RTS ، وبالتالي تفقد C3 الشحن (يرتفع VSS) بسرعة 2 مللي ثانية في المحاكاة. مواصفات الفشل 1.

- تفقد C3 الشحنة (يبدأ VSS في الارتفاع) بعد توقف نبضات الساعة عند 3.5 مللي ثانية.

- ما هو الغرض من C2 ، فهو مطلوب أصلاً؟

حلول

- من المفترض أن PICPgm يستخدم برنامج "جولة عمل". يجب أن تطبق نبضة TX طويلة للشحن المسبق إلى C2 ، ثم تدخل فقط في وضع البرمجة بعد نبضة TX الثانية؟ بالنسبة للمحاكاة ، قمت بتخفيض قيمة C2 إلى 1 فائق التوهج لإعطاء وقت ارتفاع قدره 1 مللي ثانية. ليس حلا مثاليا.

- افصل C2 و C3 بحيث يتم شحنها بشكل مستقل. تمت الإشارة إلى تعديل صغير واحد على JDM2 ، C2 إلى GND بدلاً من VSS.

- تم حلها بواسطة JDM3. يعتبر ICSP أكثر موثوقية حيث يتم تشغيل PIC بواسطة دائرة مستهدفة.

- JDM4 يحل المشكلة 1. هذا تصميم مباشر يلغي C2 تمامًا.

الخطوة 9: وأخيراً

الدليل على جودة الحلوى في أكلها. يعمل هذا JDM لذا استمر في استخدامه.

وتوصياتي هي:

- استخدم JDM2 في برمجة المقبس والمنافذ التسلسلية 12 فولت ،

- استخدم JDM4 لمبرمج ICSP والمنافذ التسلسلية أعلى +/- 9 فولت ،

- استخدم JDM4 مع إزالة وصلة المرور X2 للمنافذ التسلسلية التي تزيد عن +/- 7 فولت.

مراجع:

الأجهزة التناظرية LT التوابل

بيكبغم

فروتنبويل

تابع المزيد من مشاريع الموافقة المسبقة عن علم في الزاوية الخبيثة

موصى به:

مراجعة مجموعة Elegoo Super Started Kit Uno R3: 4 خطوات

Elegoo Super Started Kit Uno R3 مراجعة: منذ بضعة أيام ، أرسل إليجو مجموعة Super Starter Kit هذه للاختبار. لذا ، دعونا نرى ما بداخله. عند فتح هذه الحقيبة المدمجة يمكننا رؤية الكثير من الأشياء. يوجد على الغلاف فهرس بكل المكونات. في الداخل لدينا بطاقة شكر بها جميع

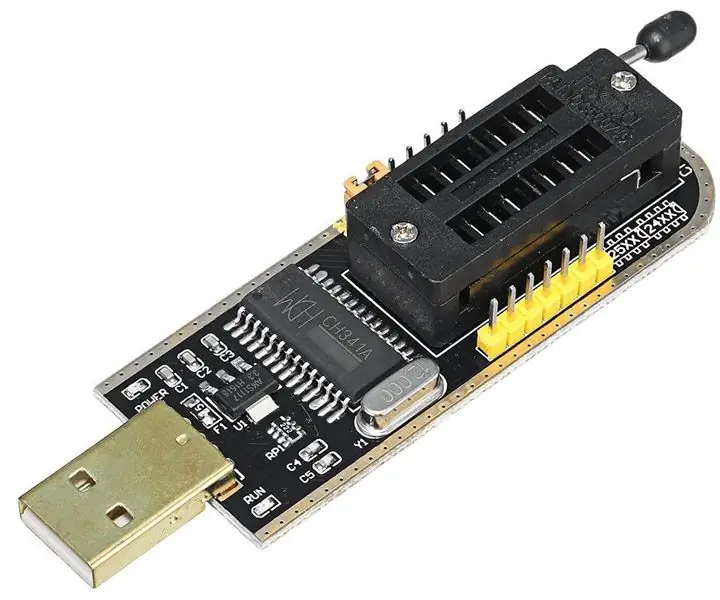

مبرمج CH341A: 8 خطوات

مبرمج CH341A: لقد اشتريت مؤخرًا مبرمج صغير CH341A. المبرمج الصغير على ما يرام ويمكن استخدامه لبرمجة رقائق سلسلة 24 و 24. إنها تكلفة منخفضة جدًا ولكنها مفيدة جدًا حيث يمكنني استخدامها لتحديث BIOS بجهاز الكمبيوتر والبرامج الثابتة لجهاز التوجيه

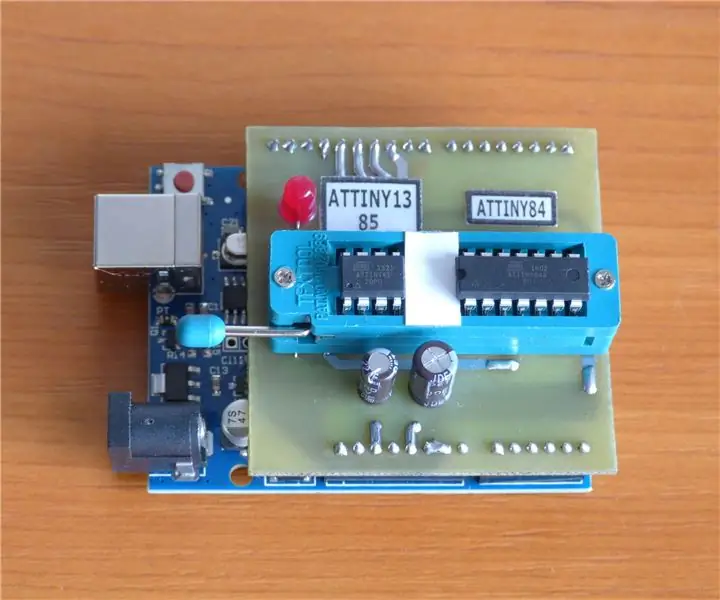

مبرمج صغير لوحدات التحكم الدقيقة ATTINY مع Arduino UNO: 7 خطوات

مبرمج صغير لـ ATTINY Microcontrollers مع Arduino UNO: من المثير للاهتمام حاليًا استخدام وحدات التحكم الدقيقة من سلسلة ATTINY نظرًا لتعدد استخداماتها وسعرها المنخفض ولكن أيضًا يمكن برمجتها بسهولة في بيئات مثل Arduino IDE. نقل بسهولة

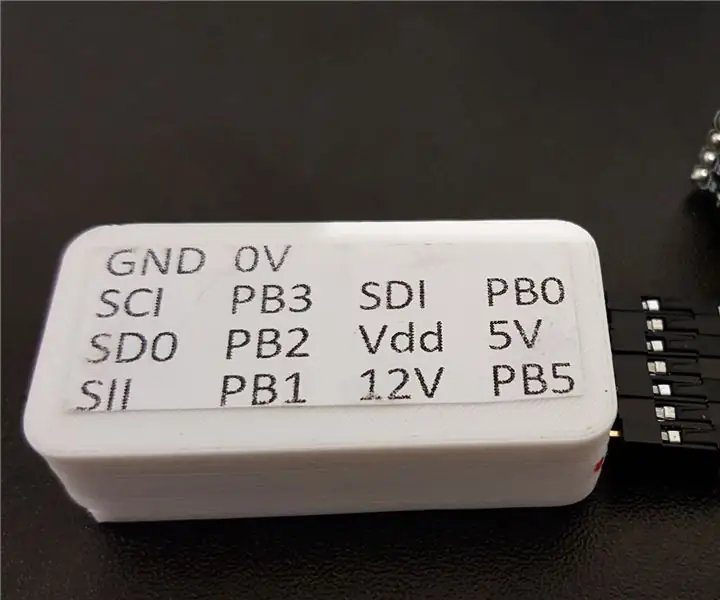

مبرمج ATTiny HV: 4 خطوات

مبرمج ATTiny HV: هذا التوجيه مخصص لأداة برمجة ATTiny باستخدام ESP8266 وواجهة مستخدم قائمة على المستعرض. يتبع ذلك من محرر Fuse السابق القابل للتوجيه لقراءة الصمامات وتعيينها ، ولكنه يدعم الآن محو وقراءة وكتابة fla

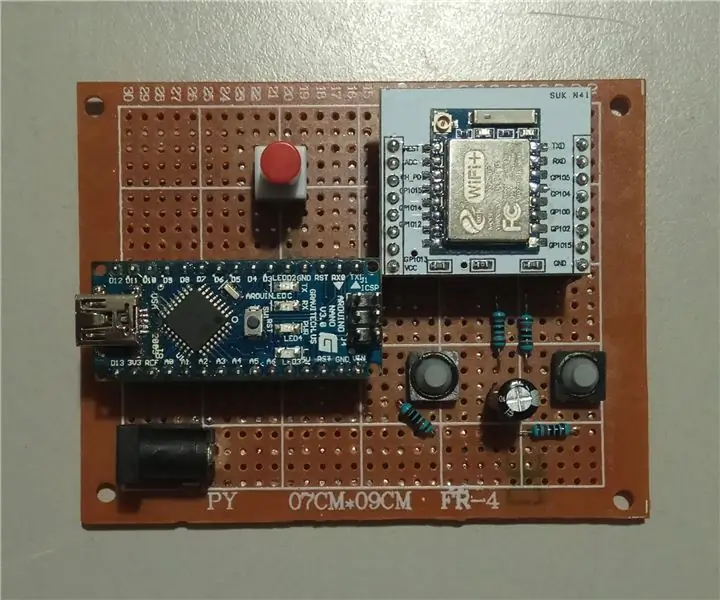

ESP8266-07 مبرمج مع Arduino Nano: 6 خطوات (بالصور)

ESP8266-07 Programmer with Arduino Nano: هذا برنامج تعليمي قصير لإنشاء لوحة برمجة ESP8266-07 / 12E أنيقة باستخدام Arduino nano. مخطط الأسلاك مشابه جدًا لتلك الموضحة هنا. لديك خيارات لتوصيل هذا المشروع بلوحة توصيل ، ولحام نفسك ب