جدول المحتويات:

- مؤلف John Day day@howwhatproduce.com.

- Public 2024-01-30 07:40.

- آخر تعديل 2025-01-23 12:54.

الهدف من هذا المشروع هو إنشاء وظيفة عرض الصور للمرآة الذكية. المرآة قادرة على عرض التوقعات (مشمس ، مشمس جزئيًا ، غائم ، عاصف ، مطر ، رعد ، وثلج) وقيم درجات الحرارة من -9999 درجة إلى 9999 درجة. يتم ترميز قيم التنبؤ ودرجة الحرارة بشكل صارم كما لو كان يتم تحليلها من واجهة برمجة تطبيقات الطقس لمحاكاة هذه القيم.

يستخدم المشروع لوحة Zynq-Zybo-7000 التي تعمل بنظام FreeRTOS ويستخدم Vivado 2018.2 لتصميم الأجهزة وبرمجتها.

القطع:

Zynq-Zybo-7000 (مع FreeRTOS)

شاشة LCD مقاس 19 بوصة (640 × 480)

كابل VGA

مرآة أكريليك مقاس 12 × 18 بوصة

الخطوة 1: تكوين Vivado

قم بتنزيل Vivado 2018.2 من Xilinx واستخدم ترخيص Webpack. قم بإطلاق Vivado و "إنشاء مشروع جديد" وقم بتسميته. بعد ذلك ، حدد "مشروع RTL" وحدد "عدم تحديد المصادر في الوقت الحالي". عند اختيار جزء ، حدد "xc7z010clg400-1" واضغط على "إنهاء" في الصفحة التالية.

الخطوة 2: تغليف VGA Driver IP

أضف ملف vga_driver.sv إلى Design Sources. بعد ذلك ، انقر فوق "أدوات" وحدد "إنشاء وحزم IP جديد". حدد "حزم مشروعك الحالي". ثم اختر موقع IP و "تضمين ملفات xci." انقر فوق "موافق" في النافذة المنبثقة ثم "إنهاء".

في "خطوات الحزم" ، انتقل إلى "المراجعة والحزم" وحدد "حزمة IP".

الآن يجب أن يكون vga_driver متاحًا ككتلة IP.

الخطوة 3: Zynq IP

ضمن قسم "IP Integrator" ، حدد "Create Block Design". أضف "نظام معالجة ZYNQ7" وانقر نقرًا مزدوجًا فوق الكتلة. انقر فوق "استيراد إعدادات XPS" وقم بتحميل ملف ZYBO_zynq_def.xml.

بعد ذلك ، ضمن "تكوين PS-PL" ، افتح القائمة المنسدلة لـ "AXI Non Secure Enablement" وحدد "واجهة M AXI GP0."

بعد ذلك ، ضمن "تكوين MIO" ، افتح القائمة المنسدلة لـ "وحدة معالج التطبيق" وحدد "Timer 0" و "Watchdog".

أخيرًا ، ضمن "تكوين الساعة" ، افتح القائمة المنسدلة لـ "PL Fabric Clocks" وحدد "FCLK_CLK0" وعند 100 ميجاهرتز.

الخطوة 4: GPIO IP

أضف كتلتين من كتل GPIO إلى تصميم الكتلة. سيتم استخدام GPIOs للتحكم في عنوان البكسل ومكونات RGB لوحدات البكسل. قم بتكوين الكتل كما هو موضح في الصور أعلاه. بمجرد إضافة وتكوين كلا الكتلتين ، انقر فوق "تشغيل أتمتة الاتصال".

تتحكم GPIO 0 - Channel 1 في عنوان البكسل وتتحكم القناة 2 في اللون الأحمر.

تتحكم GPIO 1 - Channel 1 في اللون الأخضر وتتحكم القناة 2 في اللون الأزرق.

الخطوة 5: حظر الذاكرة

أضف Block Memory Generator IP إلى Block Design وقم بتكوينه كما هو موضح أعلاه. تتم كتابة ألوان البكسل على عناوين الذاكرة التي تتم قراءتها بعد ذلك بواسطة برنامج تشغيل VGA. يجب أن يتطابق سطر العنوان مع كمية البكسل المستخدمة ، لذا يجب أن يكون 16 بت. البيانات الموجودة في هي أيضًا 16 بت نظرًا لوجود 16 بتًا لونيًا. نحن لا نهتم بقراءة أي بتات.

الخطوة 6: عنوان IP آخر

يُظهر ملف pdf المرفق تصميم الكتلة المكتمل. أضف IP المفقود وأكمل الاتصالات. أيضًا "Make Externals" لمخرجات ألوان VGA ومخرجات المزامنة الرأسية والأفقية.

xlconcat_0 - يربط بين الألوان الفردية لتشكيل إشارة RGB واحدة 16 بت يتم تغذيتها في Block RAM.

xlconcat_1 - يربط إشارات العمود والصف من برنامج تشغيل VGA ويتم إدخالها في المنفذ B من Block RAM. هذا يسمح لبرنامج تشغيل VGA بقراءة قيم ألوان البكسل.

VDD - ثابت عالي متصل بتمكين الكتابة لذاكرة الوصول العشوائي Block RAM حتى نتمكن دائمًا من الوصول إليها.

xlslice_0، 1، 2 - تُستخدم الشرائح لتقسيم إشارة RGB إلى إشارات R و G و B فردية يمكن إدخالها في مشغل VGA.

بمجرد اكتمال تصميم القوالب ، قم بإنشاء غلاف HDL وأضف ملف القيود.

* يعتمد تصميم القوالب على البرنامج التعليمي الذي كتبه benlin1994 *

الخطوة 7: SDK

تم تضمين الكود الذي يقوم بتشغيل تصميم الكتلة هذا أدناه. يحتوي Init.c على الوظائف التي تتعامل مع الرسم (التنبؤات والأرقام ورمز الدرجة وما إلى ذلك). الحلقة الرئيسية في main.c هي ما يتم تشغيله عند برمجة اللوحة. تحدد هذه الحلقة قيم التنبؤ ودرجة الحرارة ثم استدعاء وظائف الرسم في init.c. وهو يتجول حاليًا في جميع التوقعات السبعة ويعرض واحدًا تلو الآخر. يوصى بإضافة نقطة فاصل عند السطر 239 حتى تتمكن من رؤية كل صورة. تم التعليق على الكود وسوف يعطيك المزيد من المعلومات.

الخطوة 8: الخاتمة

لتحسين المشروع الحالي ، يمكن للمرء تحميل صور توقعات التحميل المسبق في أشكال ملفات COE لحظر مولدات الذاكرة. لذا فبدلاً من رسم التوقعات يدويًا كما فعلنا في كود C ، يمكن للمرء قراءة الصور. حاولنا القيام بذلك ولكن لم نتمكن من تشغيله. تمكنا من قراءة قيم البكسل وإخراجها ، لكنها خلقت صورًا فوضوية لم تكن مثل تلك التي قمنا بتحميلها على ذاكرة الوصول العشوائي. تعد ورقة بيانات Block Memory Generator مفيدة للقراءة.

المشروع هو في الأساس نصف مرآة ذكية لأنه يفتقد جانب الاتصال بالإنترنت. إضافة هذا من شأنه أن يعطي مرآة ذكية كاملة.

موصى به:

المرآة السوداء: 4 خطوات

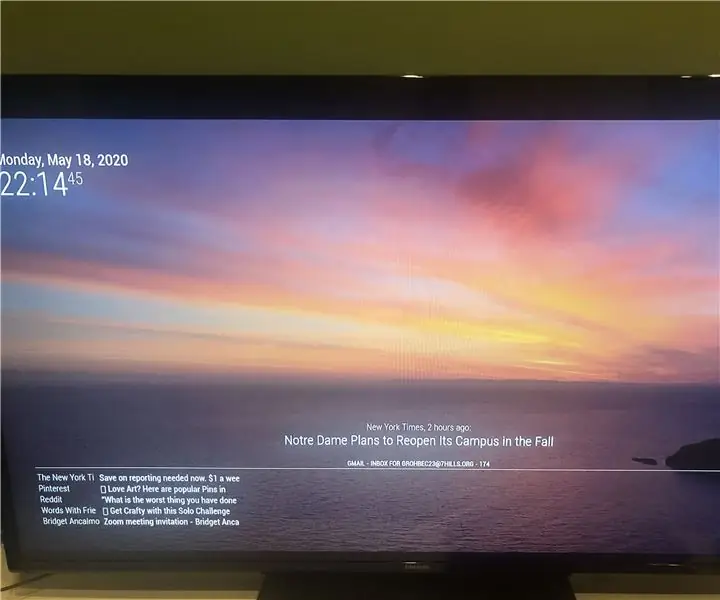

المرآة السوداء: كان هذا المشروع محاولتي لصنع مرآة ذكية. كان هدفي في هذا المشروع هو إنشاء مرآة بساعة لا تزال مرئية في المرآة. بهذه الطريقة ، عندما تستعد في الصباح ، يكون الوقت مناسبًا. حاولت أيضًا الإعلان

المرآة الذكية: 5 خطوات

Smart Mirror: ستعلمك هذه التعليمات كيفية إنشاء Smart Mirror الذي يعرض صندوق البريد الإلكتروني الخاص بك وآخر الأخبار والتحديثات من New York Times والتاريخ والوقت على خلفية من Unsplash. رابط العمل: المستلزمات المطلوبة: إطار

عرض درجة الحرارة على 3310 طريقة عرض الرسم: 5 خطوات

عرض درجة الحرارة على 3310 Display Graphic Way: مرحبًا ، أنا شديد البرودة ، لدي قناة على youtube ، لذا فإن هذا المشروع حول استخدام NOKIA 3310 DISPLAYSUPPLY: -1 X NOKIA 3310 DISPLAY (OLD / NEW ANY ONE) 1 X ARDUINO UNO / NANO (جميع الأنواع تعمل) 1X LM35 TEMP SENSOR1 X 10uf (مكثف كهربائي) بعض الأسلاك

المرآة اللامتناهية المتفاعلة للصوت: 5 خطوات

المرآة اللامتناهية المتفاعلة للصوت: في هذه التعليمات ، سأوضح لك كيف يمكنك صنع مرآة اللانهاية هذه. لذلك دعونا نبدأ

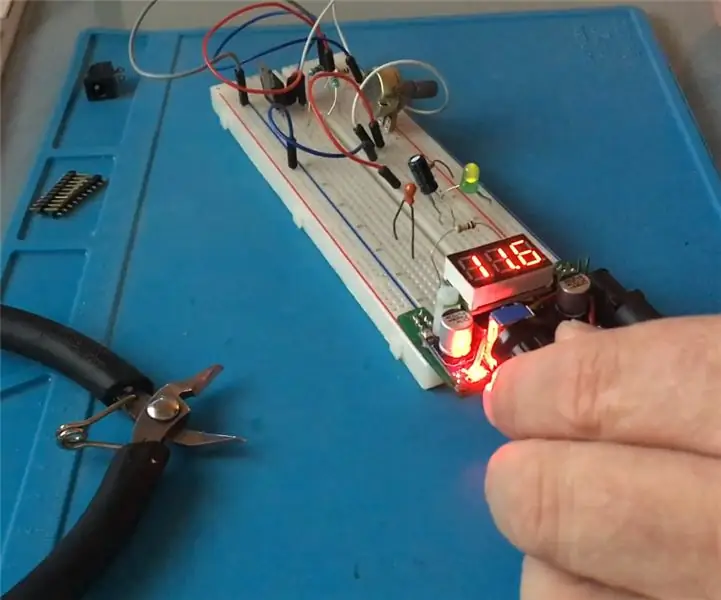

منظم جهد اللوح مع شاشة عرض / Regulador De Voltagem Com عرض Para Placa De Ensaio: 8 خطوات

منظم جهد اللوح مع شاشة عرض / Regulador De Voltagem Com Display Para Placa De Ensaio: احصل على المكونات الضرورية الموجودة في القائمة المرفقة (توجد روابط لشراء أو رؤية خصائصها). روابط نظام التشغيل ، يتم تضمينها في شكل caracteristicas د