جدول المحتويات:

- مؤلف John Day day@howwhatproduce.com.

- Public 2024-01-30 07:36.

- آخر تعديل 2025-01-23 12:53.

بواسطة AmCoderhttps://www.linkedin.com/in/mitu تابع المزيد بالمؤلف:

حول: ميتو راج - مجرد هاو ومتعلم - مصمم رقاقة - مطور برامج - متحمس للفيزياء والرياضيات المزيد عن AmCoder »

## هذا هو الرابط الأكثر شيوعًا والنقر عليه في Google لتطبيق VHDL لـ CORDIC ALGORITHM لإنشاء موجة جيبية وجيب التمام ## في الوقت الحالي ، توجد العديد من الخوارزميات الفعالة للأجهزة ، ولكنها غير معروفة جيدًا بسبب هيمنة أنظمة البرامج سنوات عديدة. CORDIC هي خوارزمية ليست سوى مجموعة من التحول والإضافة المنطقية المستخدمة لحساب مجموعة واسعة من الوظائف بما في ذلك بعض الوظائف المثلثية والقطعية والخطية واللوغاريتمية. هذه هي الخوارزمية المستخدمة في الآلات الحاسبة وما إلى ذلك. وهكذا فقط باستخدام المحولات والعناصر الإضافية البسيطة ، يمكننا تصميم جهاز أقل تعقيدًا ولكن بقوة DSP باستخدام خوارزمية كورديك. ومن ثم يمكن تصميمه كتصميم RTL مكشوف في VHDL أو Verilog دون استخدام أي وحدات فاصلة عائمة مخصصة أو عناوين IP للرياضيات المعقدة.

الخطوة 1: VHDL و Modelsim

هنا يتم تنفيذ الخوارزمية القلبية باستخدام VHDL لتوليد موجة جيبية وموجة كوز. يمكنها إخراج الجيب وجيب التمام لزاوية الإدخال بدقة كبيرة. الشفرة قابلة للتركيب على FPGA. تم استخدام Modelsim لمحاكاة التصميم ومنضدة الاختبار.

الخطوة 2: كود VHDL للتصميم ومنصة الاختبار

تستخدم تقنية القياس الثنائي لتمثيل أرقام الفاصلة العائمة.

يرجى الذهاب من خلال المستندات المرفقة قبل الرمز.

اذهب من خلال محاكاة cordic_v4.vhd - التصميم - المدخلات هي زاوية في 32 بت + بت إشارة ؛ يمكنه معالجة أي زاوية من 0 إلى +/- 360 درجة مع دقة إدخال تبلغ 0.000000000233 درجة. عند إعطاء المدخلات -> MSB هي بتة الإشارة والباقي 32 بت تمثل الحجم. - ناتج التصميم هو قيمة الجيب وجيب التمام في 16 بت + بت الإشارة. بدقة 0.00001526. يرجى ملاحظة أنه يتم عرض الإخراج في شكل مجاملة 2 إذا كانت قيمة الجيب أو جيب التمام ذات الصلة سالبة. محاكاة testb.vhd - مقعد اختبار للتصميم (1) زوايا الإدخال وإعادة تعيين السحب = '0'. بعد خطوتين من المحاكاة ، اسحب إعادة الضبط إلى "1" و "تشغيل الكل". (2) في نافذة المحاكاة ، اضبط الجذر لإشارات الخطيئة وجيب التمام على أنه رقم عشري وتنسيق> تناظري (تلقائي). [3) تصغير لرؤية شكل الموجة بصورة صحيحة.

الخطوة 3: الملفات المرفقة

(1) cordic_v4.vhd - التصميم. (2) testb.vhd - مقعد اختبار للتصميم.

(3) وثيقة حول كيفية فرض مدخلات الزاوية وتحويل النتائج الثنائية.

تحديث: هذه الملفات قديمة ولم يتم تقديمها بعد الآن. يرجى استخدام الملفات من الخطوة التالية

الخطوة 4: Mini-Cordic IP Core - 16 بت

الحد من التنفيذ أعلاه - بطيء ، وتيرة تشغيل أقل على مدار الساعة بسبب إجراء عمليات حسابية في دورة ساعة واحدة.

- مسارات حرجة موزعة على دورات متعددة لتحسين الأداء. - أسرع - تصميم FPGA تم تصنيعه حتى 100 ميجاهرتز. - مساحة أكبر محسّنة في HDL ، أجهزة أقل. - تمت إضافة إشارات حالة التحميل و Done. - الجانب السلبي فقط هو دقة أقل مقارنةً بـ السابق.

مؤتمتة بالكامل من 0 إلى 360 درجة مدخلات زاوية

الملفات المرفقة: 1) mini cordic main vhdl file2) mini cordic test bench3) mini cordic ip core manual4) doc حول كيفية فرض الزوايا وتحويل النتائج

لأية استفسارات ، لا تتردد في الاتصال بي:

ميتو راج

تابعني:

البريد: iammituraj@gmail.com

### إجمالي التنزيلات: 325 حتى 01-05-2021 ###

### تاريخ التعديل الأخير للكود: 07-يوليو -2020 ###

موصى به:

روبوت ذاتي التوازن - خوارزمية التحكم PID: 3 خطوات

روبوت التوازن الذاتي - خوارزمية التحكم PID: تم تصميم هذا المشروع لأنني كنت مهتمًا بمعرفة المزيد عن خوارزميات التحكم وكيفية التنفيذ الفعال لحلقات PID الوظيفية. لا يزال المشروع في مرحلة التطوير حيث لم تتم إضافة وحدة Bluetooth بعد والتي ستتم

الذكاء الاصطناعي للعبة الطاولة: خوارزمية Minimax: 8 خطوات

الذكاء الاصطناعي للعبة الطاولة: خوارزمية Minimax: هل تساءلت يومًا عن كيفية صنع أجهزة الكمبيوتر التي تلعب ضدها في لعبة الشطرنج أو لعبة الداما؟ حسنًا ، لا تنظر إلى أبعد من هذا Instructable لأنه سيوضح لك كيفية إنشاء ذكاء اصطناعي بسيط ولكنه فعال (AI) باستخدام خوارزمية Minimax! باستخدام ال

روبوت ذاتي الموازنة باستخدام خوارزمية PID (STM MC): 9 خطوات

روبوت ذاتي الموازنة باستخدام خوارزمية PID (STM MC): تم مؤخرًا الكثير من العمل في الموازنة الذاتية للكائنات. بدأ مفهوم التوازن الذاتي بموازنة البندول المقلوب. امتد هذا المفهوم ليشمل تصميم الطائرات أيضًا. في هذا المشروع ، قمنا بتصميم نموذج صغير

Tic Tac Toe على Arduino مع AI (خوارزمية Minimax): 3 خطوات

Tic Tac Toe على Arduino باستخدام AI (خوارزمية Minimax): في هذا Instructable ، سأوضح لك كيفية إنشاء لعبة Tic Tac Toe باستخدام الذكاء الاصطناعي باستخدام Arduino. يمكنك إما اللعب ضد Arduino أو مشاهدة Arduino يلعب ضد نفسه. أنا أستخدم خوارزمية تسمى & quot؛ خوارزمية minimax & quot ؛،

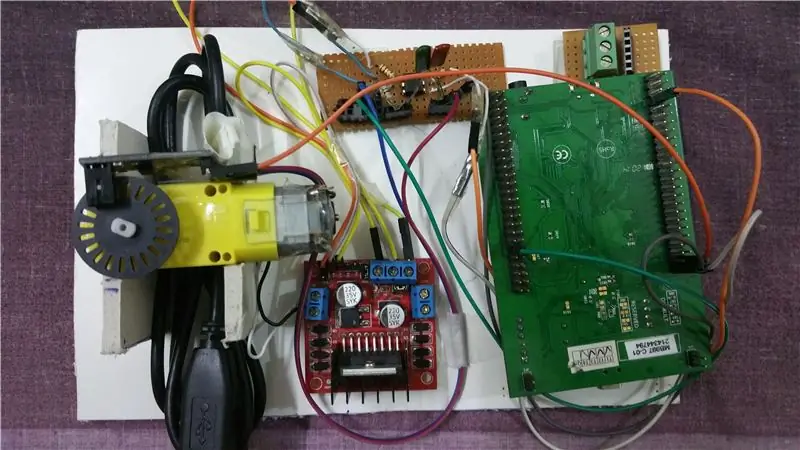

التحكم في سرعة محرك التيار المستمر باستخدام خوارزمية PID (STM32F4): 8 خطوات (بالصور)

التحكم في سرعة محرك التيار المستمر باستخدام خوارزمية PID (STM32F4): مرحبًا بالجميع ، هذا طاهر الحق مع مشروع آخر. هذه المرة هو STM32F407 كـ MC. هذا هو نهاية مشروع منتصف الفصل الدراسي. أتمنى أن تنال إعجابك ، فهي تتطلب الكثير من المفاهيم والنظريات ، لذلك نبدأ في ذلك أولاً ، مع ظهور أجهزة الكمبيوتر و