جدول المحتويات:

- الخطوة 1: ما هو Vivado HLS؟

- الخطوة 2: مكتبة الفيديو HLS

- الخطوة 3: التركيب

- الخطوة 4: تعيين الإصدار ومعلومات أخرى للتصدير

- الخطوة 5: التصدير إلى مكتبة Vivado IP

- الخطوة 6: التوليف وتحليل الصادرات

- الخطوة 7: إضافة مكتبة IP في Vivado

- الخطوة 8: إجراء ترقية

- الخطوة 9: تفاصيل ومعلومات إضافية

- الخطوة 10: الإخراج والإدخال

- الخطوة 11: واجهة تسجيل AXI

- الخطوة 12: Dataflow Pragma

- مؤلف John Day day@howwhatproduce.com.

- Public 2024-01-30 07:41.

- آخر تعديل 2025-01-23 12:54.

هل سبق لك أن أردت معالجة الفيديو في الوقت الفعلي دون إضافة الكثير من وقت الاستجابة أو في نظام مضمن؟ تستخدم FPGAs (صفائف البوابة القابلة للبرمجة الميدانية) أحيانًا للقيام بذلك ؛ ومع ذلك ، فإن كتابة خوارزميات معالجة الفيديو بلغات مواصفات الأجهزة مثل VHDL أو Verilog أمر محبط في أحسن الأحوال. أدخل Vivado HLS ، أداة Xilinx التي تسمح لك بالبرمجة في بيئة C ++ وإنشاء رمز لغة مواصفات الأجهزة منها.

البرامج المطلوبة:

- فيفادو HLS

- فيفادو

- (إذا كنت تستخدم مسجلات AXI) Vivado SDK

(اختياري) قم بتنزيل أمثلة من Xilinx هنا:

أمثلة الفيديو Xilinx HLS

الخطوة 1: ما هو Vivado HLS؟

Vivado HLS هي أداة تستخدم لتحويل كود c ++ إلى هياكل الأجهزة التي يمكن تنفيذها على FPGA ، وهي تتضمن IDE للقيام بهذا التطوير ، وبمجرد الانتهاء من تطوير كود HLS ، يمكنك تصدير IP الذي تم إنشاؤه بتنسيق للاستخدام مع فيفادو.

قم بتنزيل الملفات المرفقة وضعها بالقرب من المكان الذي ستنشئ فيه مشروعك. (أعد تسميتهم إلى "top.cpp" و "top.h" إذا كان لديهم اسم عشوائي)

الخطوة 2: مكتبة الفيديو HLS

تحتوي مكتبة فيديو HLS على وثائق ذات تصميمات مرجعية في هذه الورقة: XAPP1167 مصدر جيد آخر هو صفحة Xilinx Wiki حول هذا الموضوع.

ابدأ تشغيل Vivado HLS.

أنشئ مشروعًا جديدًا.

خذ الملفات التي قمت بتنزيلها في الخطوة السابقة وأضفها كملفات مصدر. (ملاحظة: لا يتم نسخ الملفات في المشروع ، ولكن بدلاً من ذلك تظل في مكانها)

ثم استخدم زر تصفح لتحديد الوظيفة العليا.

في الصفحة التالية ، حدد جزء Xilinx الذي تستخدمه.

الخطوة 3: التركيب

الحل => تشغيل التوليف C => الحل النشط

بعد 227.218 ثانية تقريبًا ، يجب أن يتم ذلك. (ملاحظة: سيختلف وقت التوليف الفعلي بناءً على العديد من العوامل)

الخطوة 4: تعيين الإصدار ومعلومات أخرى للتصدير

تتفاعل أرقام الإصدارات مع Vivado لتجعلك قادرًا على تحديث IP في التصميم. إذا كان تغييرًا طفيفًا في الإصدار ، فيمكن إجراؤه في مكانه بينما تتطلب تغييرات الإصدار الرئيسية منك إضافة الكتلة الجديدة يدويًا وإزالة القديم. إذا لم تتغير واجهاتك وكان تحديث الإصدار بسيطًا ، فيمكن أن يكون التحديث يتم ذلك تلقائيًا تمامًا عن طريق الضغط على زر تحديث IP. يمكنك تشغيل "report_ip_status" في وحدة تحكم Vivado tcl لمعرفة حالة عنوان IP الخاص بك.

عيّن أرقام الإصدارات والمعلومات الأخرى في الحل => إعدادات الحل …

بدلاً من ذلك ، يمكن ضبط هذه الإعدادات أثناء التصدير.

الخطوة 5: التصدير إلى مكتبة Vivado IP

الحل => تصدير RTL

إذا لم تقم بتعيين تفاصيل مكتبة IP في الخطوة السابقة ، فيمكنك القيام بذلك الآن.

الخطوة 6: التوليف وتحليل الصادرات

في هذه الشاشة ، يمكننا رؤية الإحصائيات المتعلقة بالوحدة التي تم تصديرها ، والتي توضح أنها تفي بفترة ساعتنا البالغة 10 نانو ثانية (100 ميجاهرتز) ومقدار كل مورد تستخدمه.

مع مزيج من هذا ، تقريرنا التجميعي ، وتحليل تدفق البيانات لدينا ، يمكننا أن نرى أن الأمر يستغرق 317338 دورة على مدار الساعة * فترة ساعة 10ns * 14 مرحلة خط أنابيب = 0.04442732 ثانية. بمعنى أن الكمون الإجمالي الذي تمت إضافته من خلال معالجة الصور لدينا أقل من جزء واحد من عشرين من الثانية (عندما يتم تسجيله عند 100 ميجاهرتز المستهدف).

الخطوة 7: إضافة مكتبة IP في Vivado

لاستخدام كتلة IP المركبة الخاصة بك ، ستحتاج إلى إضافتها إلى Vivado.

في Vivado ، أضف مستودع IP إلى مشروعك بالانتقال إلى كتالوج IP والنقر بزر الماوس الأيمن فوق تحديد "Add Repository …"

انتقل إلى دليل مشروع Vivado HLS وحدد دليل الحلول الخاص بك.

يجب أن يبلغ عن عنوان IP الذي وجده.

الخطوة 8: إجراء ترقية

تحتاج أحيانًا إلى إجراء تغييرات على كتلة HLS بعد تضمينها في تصميم Vivado.

للقيام بذلك ، يمكنك إجراء التغييرات وإعادة تركيب وتصدير IP برقم إصدار أعلى (راجع التفاصيل في الخطوة السابقة حول التغييرات الرئيسية / الثانوية في رقم الإصدار).

بعد تغيير تصدير الإصدار الجديد ، قم بتحديث مستودعات IP الخاصة بك في Vivado. يمكن القيام بذلك إما عندما يلاحظ Vivado أن IP قد تغير في المستودع ، أو يتم تنشيطه يدويًا. (ملاحظة ، إذا قمت بتحديث مستودعات IP الخاصة بك بعد البدء ، ولكن قبل اكتمال التصدير في HLS ، فلن يكون IP موجودًا مؤقتًا ، وانتظر حتى ينتهي ثم التحديث مرة أخرى.)

في هذه المرحلة ، يجب أن تظهر نافذة تحتوي على المعلومات التي تفيد بأن IP قد تم تغييره على القرص وتمنحك خيار تحديثه باستخدام زر "Upgrade Selected". إذا كان التغيير عبارة عن تغيير بسيط في الإصدار ولم يتم تغيير أي من الواجهات ، ثم يؤدي الضغط على هذا الزر إلى استبدال عنوان IP القديم تلقائيًا بالعنوان الجديد ، وإلا فقد يتطلب الأمر المزيد من العمل.

الخطوة 9: تفاصيل ومعلومات إضافية

توفر الخطوات التالية مزيدًا من المعلومات حول كيفية عمل توليف HLS وما يمكنك فعله به.

للحصول على مثال لمشروع يستخدم كتلة IP مركبة HLS ، راجع هذا الدليل.

الخطوة 10: الإخراج والإدخال

يتم تحديد المخرجات والمدخلات إلى كتلة IP النهائية من تحليل يقوم به المركب لتدفق البيانات داخل وخارج الوظيفة العليا.

على غرار VHDL أو verilog ، يتيح لك HLS تحديد تفاصيل حول الاتصالات بين IP. هذه السطور هي أمثلة على ذلك:

تم إلغاء تصفية image_filter (AXI_STREAM & video_in، AXI_STREAM & video_out، int & x، int & y) {

#pragma HLS INTERFACE axis port = video_in bundle = INPUT_STREAM #pragma HLS INTERFACE port = video_out bundle = OUTPUT_STREAM #pragma HLS INTERFACE منفذ s_axilite = x bundle = CONTROL_BUS offset = 0x14 # pragma HLS INTERFACE

يمكنك أن ترى كيف تتأثر المنافذ المعروضة على كتلة IP بهذه التوجيهات.

الخطوة 11: واجهة تسجيل AXI

من أجل الحصول على الإدخال / الإخراج من / إلى كتلة IP الخاصة بك إلى PS ، فإن الطريقة الجيدة للقيام بذلك هي من خلال واجهة AXI.

يمكنك تحديد هذا في كود HLS الخاص بك ، بما في ذلك الإزاحات التي سيتم استخدامها للوصول إلى القيمة لاحقًا كما يلي:

تم إلغاء تصفية image_filter (AXI_STREAM & video_in، AXI_STREAM & video_out، int & x، int & y) {

#pragma HLS INTERFACE منفذ s_axilite = x حزمة = CONTROL_BUS offset = 0x14

#pragma HLS INTERFACE منفذ s_axilite = y bundle = CONTROL_BUS offset = 0x1C #pragma HLS dataflow

س = 42 ؛

ص = 0xDEADBEEF ؛ }

بمجرد الاتصال بشكل صحيح في Vivado ، يمكنك الوصول إلى القيم باستخدام هذا الرمز في Vivado SDK:

# تضمين "parameters.h"

#define xregoff 0x14 # تعريف yregoff 0x1c x = Xil_In32 (XPAR_IMAGE_FILTER_0_S_AXI_CONTROL_BUS_BASEADDR + xregoff) ؛ y = Xil_In32 (XPAR_IMAGE_FILTER_0_S_AXI_CONTROL_BUS_BASEADDR + yregoff) ،

سيؤدي هذا إلى حصولك على 42 في x و 0xdeadbeef في y

الخطوة 12: Dataflow Pragma

داخل #pragma DATAFLOW ، تتغير طريقة تنفيذ الكود من C ++ العادي. الكود موصول بالأنابيب بحيث يتم تشغيل جميع التعليمات في جميع الأوقات في أجزاء مختلفة من البيانات (فكر في الأمر كخط تجميع في مصنع ، تعمل كل محطة بشكل مستمر في أداء وظيفة واحدة وتمريرها إلى المحطة التالية)

من الصورة يمكنك أن ترى أن كل من التوجيهات

على الرغم من ظهورها على أنها متغيرات عادية ، إلا أن كائنات img يتم تنفيذها فعليًا كمخازن مؤقتة صغيرة بين الأوامر. إن استخدام صورة كمدخل لوظيفة "يستهلكها" ويجعلها غير قابلة للاستخدام. (ومن هنا جاءت الحاجة إلى الأوامر المكررة)

موصى به:

Ultimate Knife Block: 11 خطوة (بالصور)

The Ultimate Knife Block: لقد كنا جميعًا هناك ، ونقطع الخضار بسكين غير حاد ، وسيكون استخدام ملعقة صغيرة أكثر فاعلية. في تلك اللحظة ، تفكر في كيفية وصولك إلى هناك: كانت سكاكينك حادة مثل شفرات الحلاقة عندما اشتريتها ولكن الآن ، بعد ثلاث سنوات ،

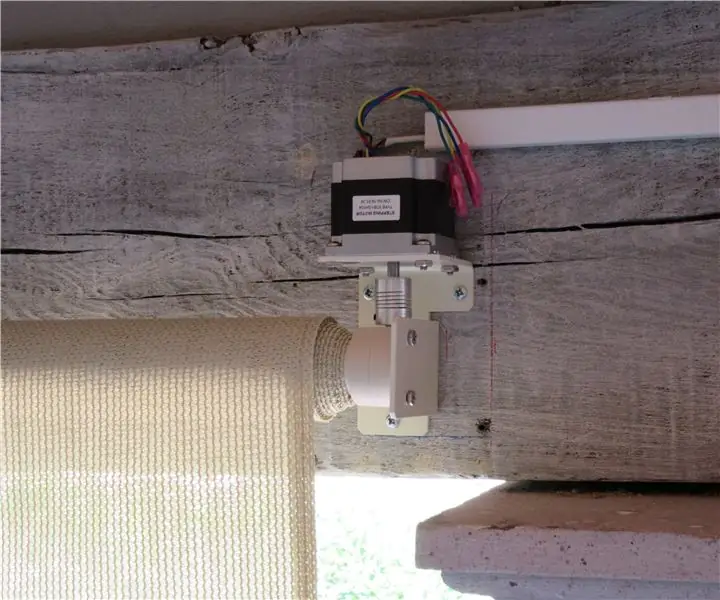

اختيار محرك خطوة ومحرك لمشروع شاشة الظل الآلي في Arduino: 12 خطوة (بالصور)

اختيار Step Motor و Driver لمشروع شاشة الظل الآلي من Arduino: في هذا Instructable ، سأنتقل إلى الخطوات التي اتخذتها لتحديد Step Motor و Driver لمشروع نموذج شاشة الظل الآلي. شاشات الظل هي طرازات Coolaroo ذات الكرنك اليدوية الشائعة وغير المكلفة ، وأردت استبدال

ماسح سيكلوب ثلاثي الأبعاد My Way خطوة بخطوة: 16 خطوة (بالصور)

Ciclop 3D Scanner My Way خطوة بخطوة: مرحبًا بالجميع ، سأدرك ماسح Ciclop ثلاثي الأبعاد الشهير ، كل الخطوات الموضحة جيدًا في المشروع الأصلي غير موجودة ، لقد قمت ببعض الإصلاح لتبسيط العملية ، أولاً أقوم بطباعة القاعدة ، وأعيد ضبط ثنائي الفينيل متعدد الكلور ، لكن استمر

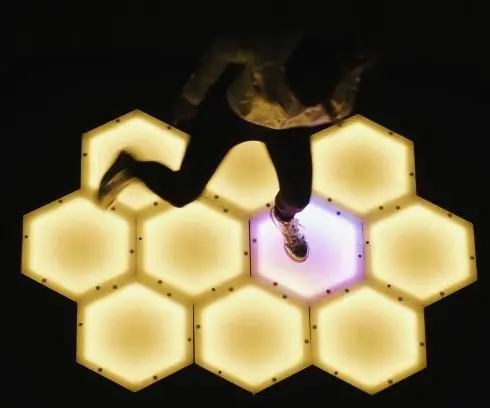

واجهة خطوة MIDI (نسخة باللغة الإسبانية): 12 خطوة

MIDI Step Interface (versión En Español): Versión en inglés aquí.En este التعليمي te mostraremos cómo hacer una plataforma التفاعلية de luz y sonido، que puede ser usada para jugar el famoso “Simon Says” al igual que como un controlador MIDI. أمبوس أساليب الأوبرا تخدع الفطائر

كيفية استخدام Vivado Simluation: 6 خطوات

كيفية استخدام Vivado Simluation: لقد أنجزت مشروع المحاكاة هذا لفصل عبر الإنترنت. تمت كتابة المشروع بواسطة Verilog. سنستخدم المحاكاة في Vivado لتصور شكل الموجة في enable_sr (تمكين الرقم) من مشروع ساعة الإيقاف الذي تم إنشاؤه مسبقًا. بالإضافة إلى ذلك ، سوف نقوم